| 编辑推荐: |

本文主要介绍了软件定义硬件的设计开发测试的左移等相关内容。希望对你的学习有帮助。

本文来自于微信公众号软件定义战争,由火龙果软件Linda编辑、推荐。 |

|

大家都知道,讲军用 CPS(赛博物理系统)系统 DevOps 的书很少。诺格和洛马两位敏捷实践专家联袂写过一本。不过作者诚意不足,里面干货不多。这本书第十一章主题就是左移,不过就讲了点概念,讲的太浅。这个也可以理解,这个行业的东西可不兴随便乱讲。

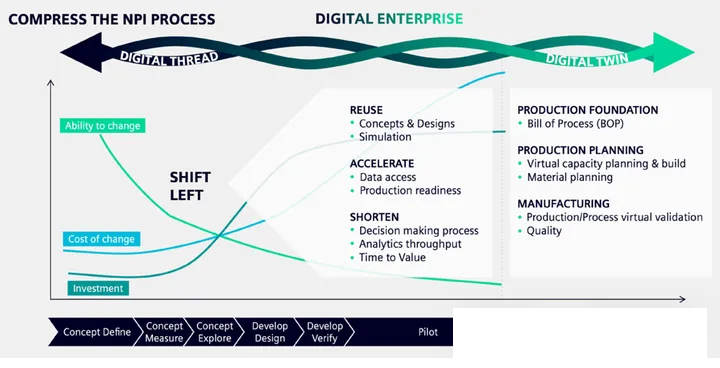

不过好消息是,军用系统的 DevOps 也是民转军的(从该书每章的引用文献可以看出),我们研究 Vee

模型的坍缩、Vee 模型的左移(shift left)、测试评估连续统的快速、持续的反馈环、Vee模型右侧的V&V(验证和确认)嵌入

CI/CD(持续集成/持续交付)等,也可以从民用源头上去寻找。

基于这个想法,为了深入理解系统工程 Vee 模型的左移,就找了一些民用的左移案例研究下。这些案例,对军用系统这种硬件为主的组织,相信会有一些启发。

所以最近花了一周多时间打窝,搜集了几十个不同领域左移案例的素材。本文从中整理了十个硬件设计开发测试左移的案例。软件设计开发测试的左移案例,以及军事领域的左移案例,后续再介绍。

1. 什么是左移?

可能有些读者还不知道什么是左移。我们直接讲两个左移的实际例子,这样子最直观。一个是软件测试的左移;另一个是半导体行业EDA设计测试验证的左移。

1.1 软件测试的左移

我们先从软件测试左移讲起。因为它是最广为人知的左移。

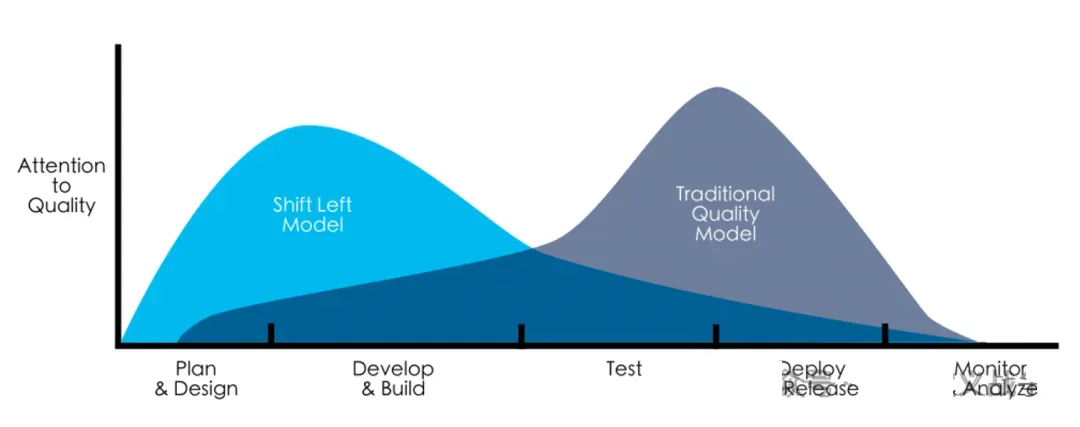

软件测试左移是一种测试理念,将测试阶段从软件开发生命周期的末端转移到初始阶段。它遵循了“一盎司的预防胜过一磅的治疗”的原则,即尽量及早发现问题,因为越早发现问题,解决起来更容易成本也更低,而且影响也更小。

传统的软件测试范式,其测试活动都是在软件开发构建完成之后才开始。这种方式会带来各种软件质量和性能问题,从而降低产品交付速度、需求变更难以应对以及缺乏持续、及时的反馈机制等问题。

测试左移这种新的测试范式,则是提前进行测试活动、加强开发人员和测试人员的协作以及采用自动化测试等方法。

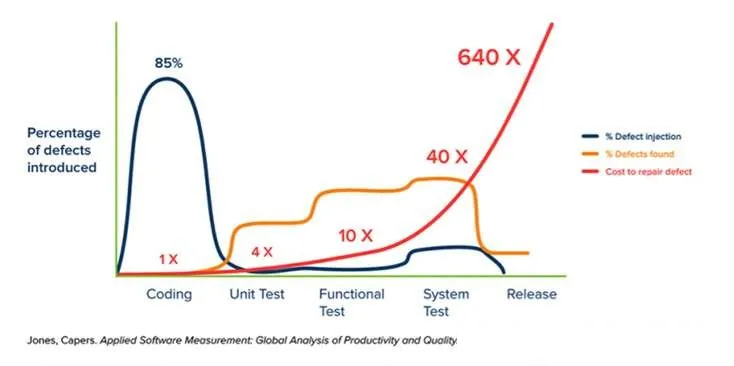

测试左移的主要驱动力是因为大部分缺陷都是在项目前期引入的。这些缺陷发现地越晚,修复缺陷的代价就越高。通过左移,可以在早期阶段发现和解决软件缺陷。

1.2 EDA的左移

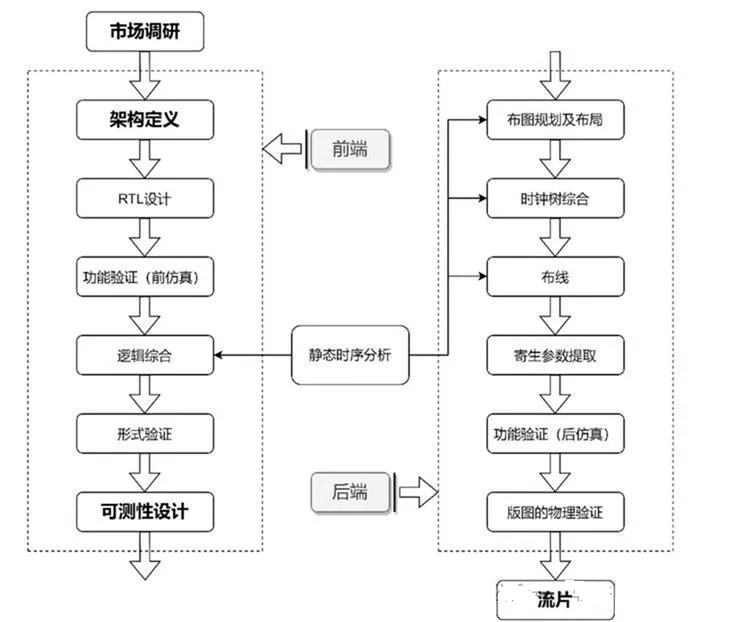

电子设计自动化 (electronic design automation, EDA) 是集成电路(IC)领域的关键技术之一。随着集成电路的规模快速增长,芯片的晶体管数则达到了百亿级别,例如

NVIDIA公司推出的 H100 GPU 拥有 800 亿个晶体管。由于电路规模的庞大,集成电路的设计、验证、制造的流程越来越复杂(下图),靠人工是完全不够的,需要计算机来辅助。

计算机辅助集成电路的辅助设计有三大秘密武器。

编程语言:用编程语言来设计芯片,这个是米德和康威提出的芯片设计历史上的最重要思想之一。

EDA 工具:人和动物的区别是会造工具。各种纷繁复杂的设计、验证和制造环节的工作,都交给高效强大的

EDA 工具来完成。

复用已有的成熟设计模块,形成良好的硬件设计生态。比如 ARM 公司提供的 IP。

在这三个中间,EDA 工具处于核心地位。但是传统的 EDA 工具受到传统的瀑布式的集成电路开发模型的影响很大,带来了一系列的问题。

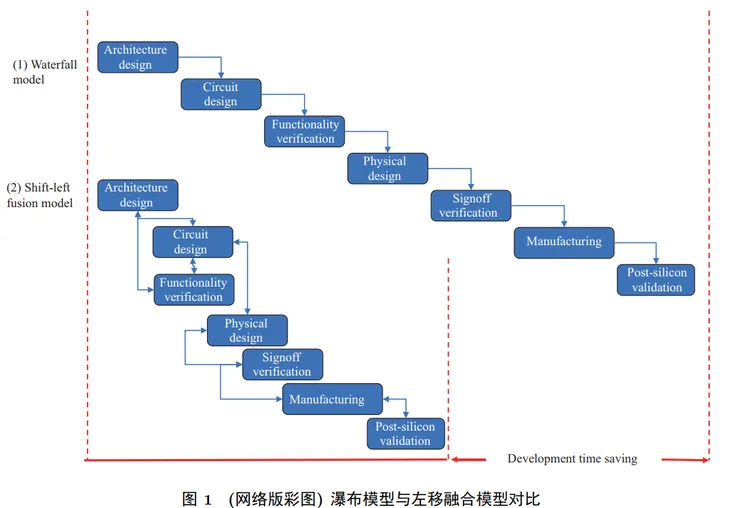

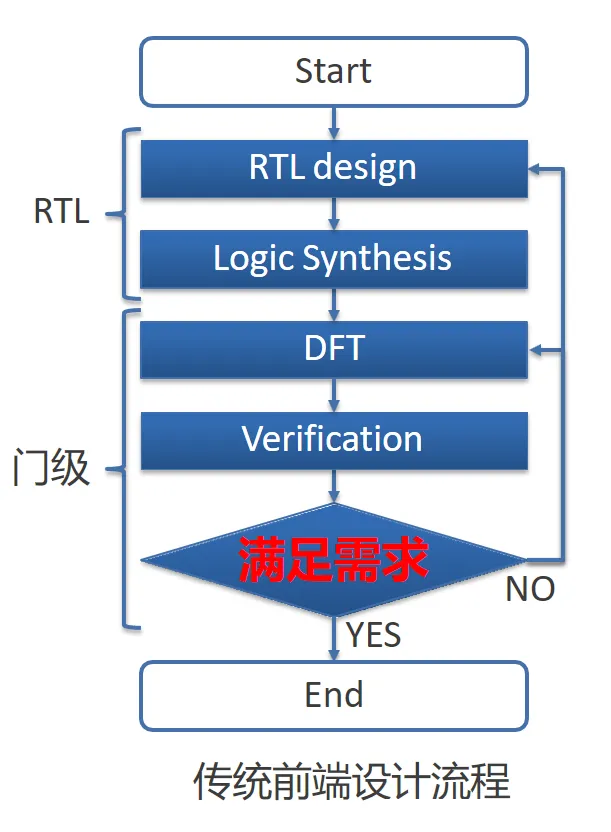

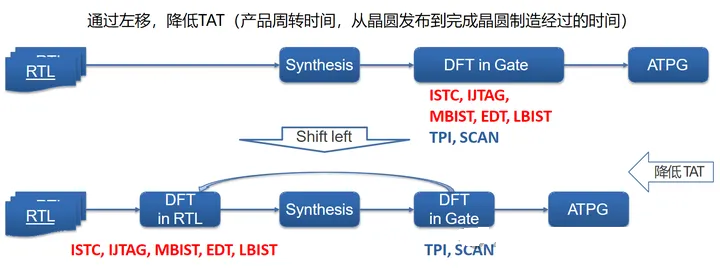

在论文《EDA 左移融合设计范式的发展现状、趋势与挑战》中,就对 EDA 的瀑布模型和左移融合模型(下图)进行了对比分析。

这篇论文对比了传统瀑布式EDA流程和左移融合的EDA流程的优缺点。

传统 EDA 流程采用瀑布模型 (waterfall model) 的设计范式,即将设计流程顺序地划分为若干个阶段,

实现阶段间的解耦与设计流程的简化。在瀑布模型中, 设计流程是完全串行的,前一个阶段完成后才可以开始后一个阶段,从而确保了阶段的独立性。虽然这一设计范式降低了每一个阶段的复杂性,但是却带来了整体迭代周期的延长,并且阻止了全局优化,导致优化不足。

左移融合模型是一种新兴的 EDA 设计范式。该概念指将设计过程的关注点从瀑布模型的顺序流程转向更早期的设计阶段。左移要求开发流程的不同阶段强化协作,包括但不限于:

- 早期对传统流程后期出现的事项进行估算和协同设计,缩短设计周期并提升性能;

- 在早期阶段进行测试及分析,尽早发现和预防问题, 提高芯片的质量和效率,实现降本增效;

- 开发模型或抽象以支持设计阶段的并行开展,通过开发流程的左移,实现了流程的并行化,充分利用流程前期的低修复成本与高优化空间,从而缩短了开发周期,降低开发成本。

这篇论文盘点了多个 EDA 公司已经推出的基于左移的 EDA 产品,比如:

Synopsys Platform Architect:提供了基于 SystemC TLM 的工具和高效的方法,

供架构师和系统设计师用于早期分析和优化多核 SoC (system on chip) 架构的性能和功耗;

DSO.ai:通过人工智能、强化学习, 在芯片设计的庞大解决方案空间中寻找优化目标,实现 RTL

到 GDSII 的全流程自动优化;;

Virtualizer Development Kits (VDKs): 支持特定设计的虚拟原型、调试和分析工具,

以及软件开发工具包, 使软件开发不依赖于 RTL 设计而能够在设计周期中提前进行;

Cadence 的 Joules RTL Design Studio:支持设计在布局布线阶段之前进行更准确的功耗、性能、面积和物理设计拥塞分析.;

JedAI:支持提取不同阶段的设计数据, 工作流数据和工作负载数据, 通过数据分析以在设计早期预测设计结果.;

Siemens的 Calibre Design Solutions:通过将设计阶段与制造良率检查融合,

实现在设计早期发现潜在的制造坏点以指导物理设计, 缩短上市时间。

这篇论文对这些左移的 EDA 产品的左移的侧重点进行了分析,指出它们之间侧重点都不同——“比如 Synopsys

注重于数据模型的共享而非抽象层次的改变,将不同阶段的技术提前应用并融合到设计流程,同时还提供后端阶段前端化,以实现最终的性能、功耗、面积

(PPA) 优化。Siemens 则强调利用新工具和语言帮助弥合不同抽象层次的差距。”

2. 为什么需要左移?

要理解为什么需要左移,最直观的方式就是看现实世界中,如果没有采用左移,会对软设计开发和硬件设计开发造成的影响。

加拿大原子能有限公司(AECL)Therac-25,属于第三代医用高能电子直线加速器,由于其软件设计存在瑕疵,软件的互锁机制缺陷,用户界面问题,工程师重用了之前型号的软件代码,但没有进行充分的验证和测,造成多位患者死亡或严重辐射灼伤。

阿丽亚娜5号火箭发射40秒后姿态失控后自毁,上面的卫星没有投保,损失5亿美元。原因是阿丽亚娜5号移植自阿丽亚娜4号上的64位浮点数转16位有符号整数的代码没有测试,而阿丽亚娜5号速度更快,导致超出了16位有符号整数的存储范围。

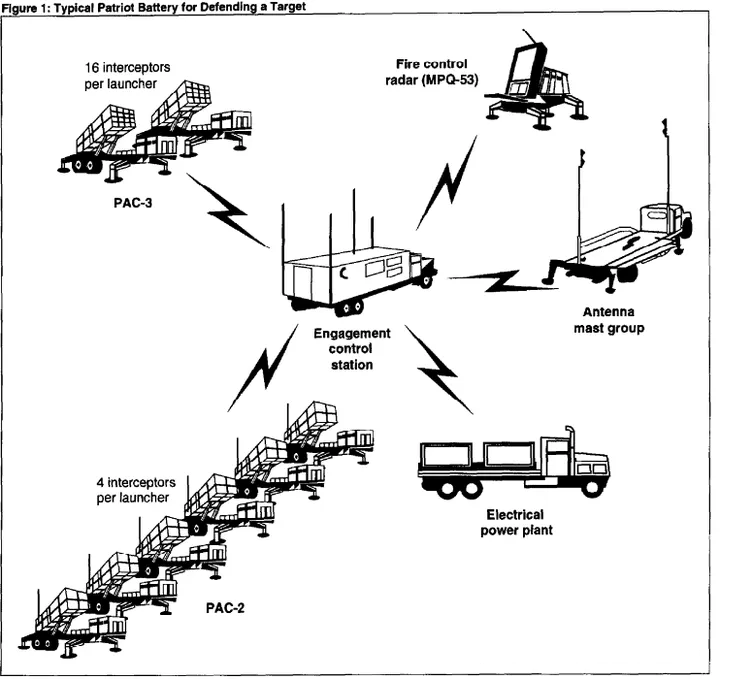

海湾战争期间,爱国者导弹连续运行上百小时,系统时间累积误差放大,导致没有击落伊拉克的飞毛腿导弹,28名美陆军士兵被炸死。

Nicely 发现英特尔奔腾芯片的浮点数计算缺陷,造成英特尔 CPU 产品推迟发布数月,损失5亿美元。

软硬件原因导致的汽车召回所占的比例,最近十年以来,从12%上升到24%。通用汽车刹车软件缺陷,召回45万辆车。丰田ECU软件缺陷。美洲虎无法关闭巡航控制系统软件故障,召回近18000辆X型汽车。Robotaxi

软件算法缺陷。特斯拉摄像头算法召回。小米汽车自动泊车算法出现问题,被迫召回。

如果没有 EDA 工具的左移,那么设计测试效率就会大大降低,产品上市时间延后半年到2年不等。

对于软件定义的武器系统,以及软件定义 AI 赋能的杀伤链来说,软件的缺陷应该和越来越复杂的汽车或者芯片一样,也会指数升高。对武器系统的测试评估成本更高耗时更长。

下面我们看爱国者vs飞毛腿导弹的软件缺陷的分析。

爱国者导弹系统最大的系统级的失效,发生在1991年2月25日夜里。发射自伊拉克的一枚飞毛腿导弹击中了一个位于沙特阿拉伯达兰的美陆军营房,造成28名士兵死亡100多人受伤,而防卫这片区域的爱国者导弹连A连并没有对到来的飞毛腿导弹开火。

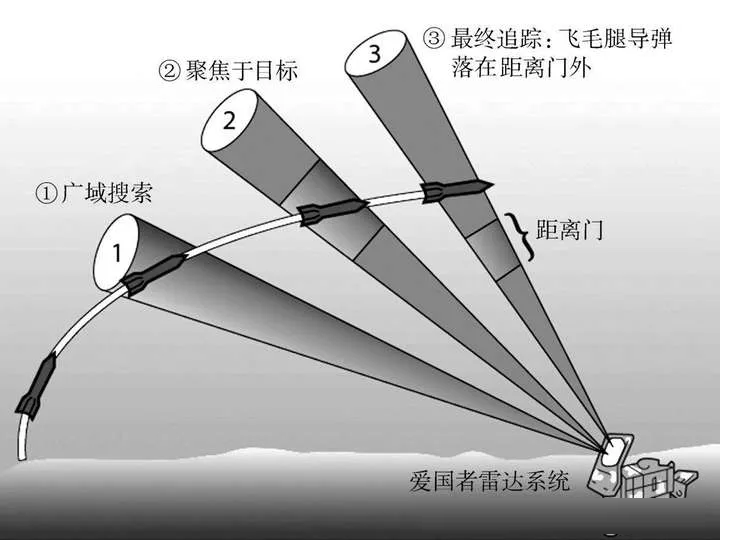

在飞毛腿导弹出现在火控雷达广域搜索视野中时,爱国者导弹系统的确检测到了它的出现。然而在最终目标跟踪阶段,系统却出现了致命的错误。在爱国者火控雷达的最后跟踪阶段,只有在距离门中的雷达回波才会被处理,然后触发发射拦截弹摧毁来袭目标的指令。而当天计算机程序由于计算距离门错误,扫描了错误的距离门,导致火控雷达没有跟踪到来袭目标,从而没有发射爱国者导弹。

这次失败的拦截,经过分析,根因是一个软件错误。这个软件错误导致目标没有进入爱国者火控雷达的距离门,导致目标检测失败(下图)。①雷达广域搜索到飞毛腿导弹来袭。②雷达聚焦于设定的目标。③软件计算距离门的累积错误使系统产生错误的距离门。由于飞毛腿导弹并没有飞经距离门,因此雷达就没有检测到目标,就没有发射爱国者的拦截弹。

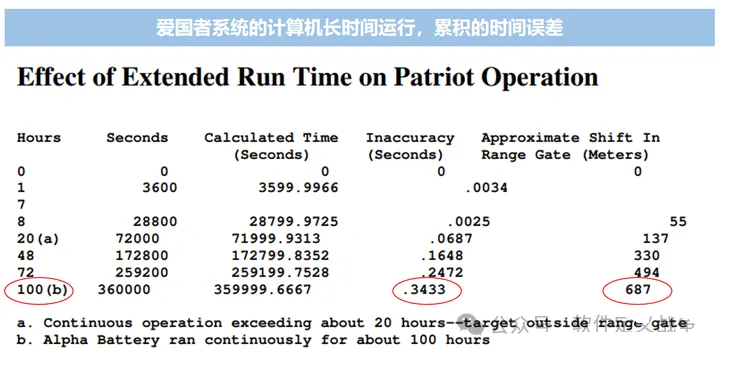

为什么程序会扫描错误的距离门呢?距离门的计算依赖于根据系统内部时钟计算的时间。在这个计算过程中,需要把系统时间乘以1/10。而这个计算过程是用24位的定点寄存器存储的。在计算机里无法保存真正的实数,是用有限位精度的二进制的小数去逼近的。

1/10 用二进制表示的话,就是0.0001100110011001100110011001100.....

在跟踪系统计算机里的24位定点寄存器中,由于只有24位宽,1/10 被截断表示为0.00011001100110011001100,截断误差为0.0000000000000000

000000011001100...。这个阶段误差换算成十进制,就是0.000000095。随着系统的运行,越来越多的截断错误在累加。

爱国者导弹系统如果连续运行20小时,目标和距离门的偏差就会达到50%,导致雷达搜索区域偏离目标。达兰的爱国者导弹防空连A连(Alpha

Battery)已经连续运行了100个小时。所以时间累积误差是 0.000000095(每秒的截断误差)×100(小时)×60(分钟)×60(秒)×10(因为之前乘以了1/10)≈

0.34(秒)。

累积的时间误差,使实际时间和计算出的时间相差了0.3433秒。因为飞毛腿导弹飞行的速度5个马赫(1676米/秒),0.3433秒的时间误差使跟踪距离偏离了687米,这一距离已经大到不能正确检测到飞毛腿导弹了。

3. 硬件左移案例汇总清单

接下来,我给大家介绍10个精选的硬件左移的案例,其中大都是相应行业的领先企业的实际解决方案。

软硬件协同开发测试的左移(英特尔)

云计算硬件测试评估的左移(微软 Azure)

高速 PCB 电路设计测试的左移(Cadence)

RTL 测试的左移(瑞萨)

FPGA 和 SoC 设计测试的左移(Xilinx)

汽车 ECU 软硬件协同设计开发测试的左移(Synopsys)

多模态EDA设计的左移(香港中文大学、北大、华为等)

射频设计的左移(Keysight)

多物理仿真的左移(Cadence)

电子产品测试的左移:电子代工厂测试的左移(苹果/富士康/捷普),半导体制造的左移(西门子)

4. 硬件左移十大案例

4.1 软硬件协同开发下的左移(英特尔)

提出厂商:英特尔

左移对象:基于硬件的软件开发

左移方式:通过虚拟硬件仿真器,让软件可以在硬件还没有准备好的情况下进行开发和测试

左移价值:缩短产品上市时间

我们通常所说的左移,源自2001年 Larry Smith 提出的测试左移这个概念。然后才有了安全左移等其他左移的实践。

但是严格来说,左移这个理念,其实更早的时候就有了。典型的例子就是基于英特尔的Simics仿真器的软硬件协同开发。它虽然是2002年提出来的,但是实际上应该在更早的时候就在内部研究了。当然英特尔的这个左移,针对的是硬件开发测试的左移。

FPGA厂商的SoC FPGA 硬件就像武器装备一样,在进入全速生产之前,用户很难获得相应的产品。此外,就算

FPGA 硬件已经上市,相应的评估板和开发板也要滞后一到两个季度。基于 FPGA产品进行二次开发的公司,等拿到评估板开发板再进行开发,还要一段时间。如果这些二次开发的公司,能够在拿到评估板开发板之前,通过虚拟硬件平台进行开发测试,就可以将他们的基于FPGA厂商提供的硬件开发的产品上市时间大大缩短,从而在市场上获取先发优势和更多利润。

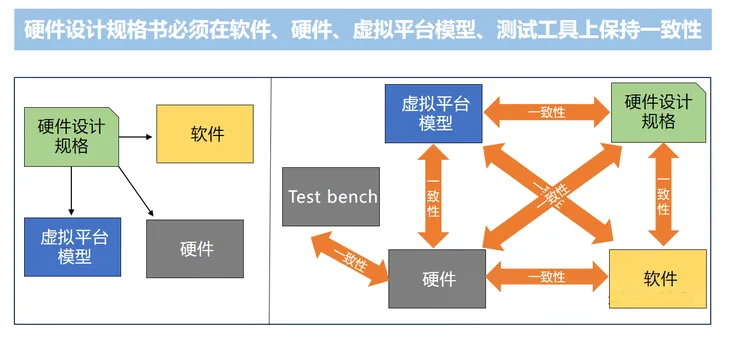

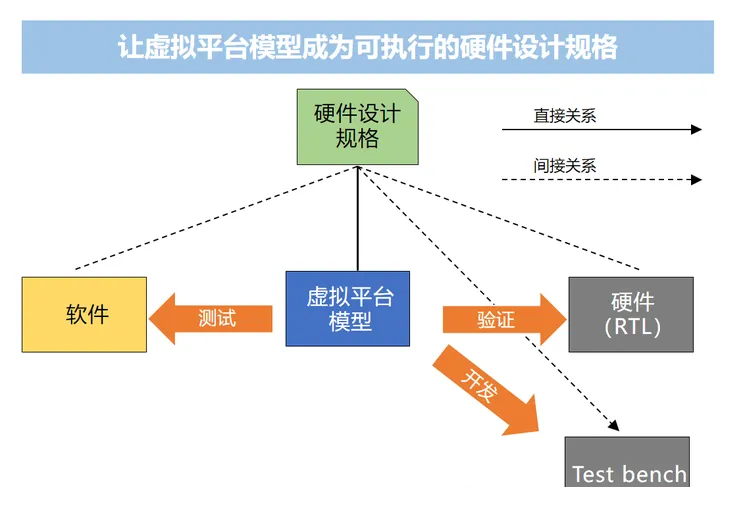

但是这里面还存在一个问题。硬件设计规格书必须在软件、硬件、虚拟平台模型、测试工具上保持一致性。但是传统的方式之下,要维护这四者之间的一致性,是点对点方式实现的。

解决方案就是用虚拟平台模型成为可执行的硬件设计规格,基于虚拟平台模型用 Test bench 测试工具开发测试代码,然后对软件进行测试、对硬件进行验证。软件、硬件和测试,与硬件设计规格就解耦了,从而大大减轻了软件、硬件、测试团队维护和硬件设计规格一致性的繁杂工作。

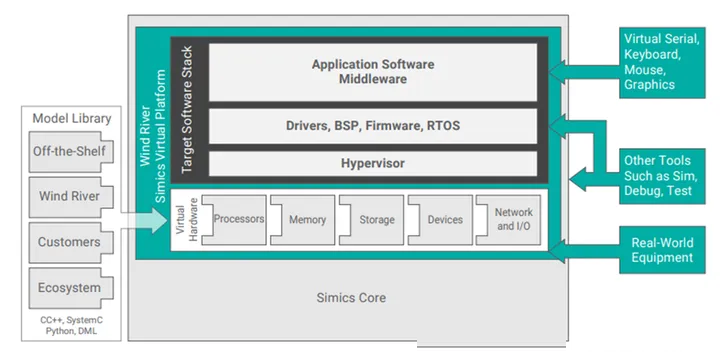

英特尔的Simics仿真软件,是一个从芯片到系统的虚拟平台。Simics 提供 DML 设备建模语言,开发者可以在没有实际硬件的情况下,对硬件进行虚拟建模,然后对软硬件系统进行全面的验证和测试。DML

与 Simics 仿真软件之间存在紧密的关系,它们共同构成了英特尔在硬件建模与仿真领域的强大工具链。通过DML定义的设备模型与Simics仿真环境的结合,开发者可以更加高效地进行硬件系统的建模、仿真、测试和优化工作,从而加速产品开发和上市时间并降低开发成本。

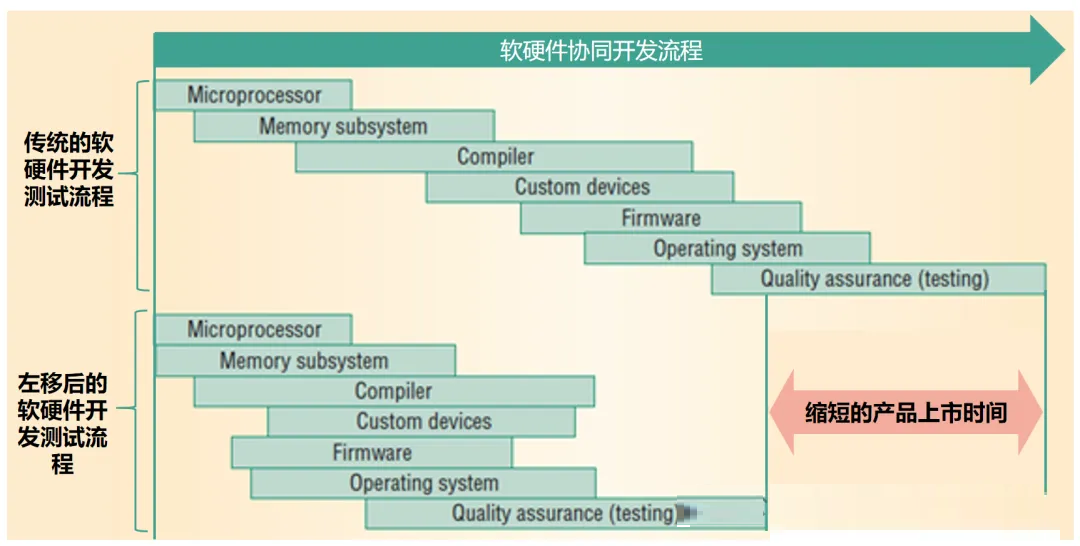

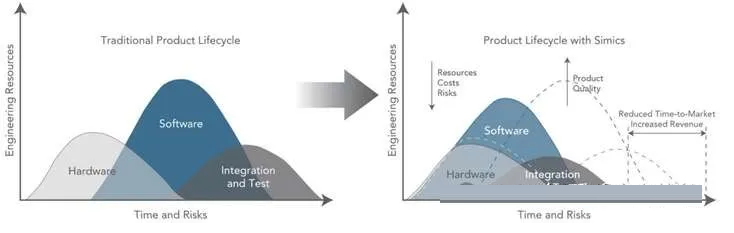

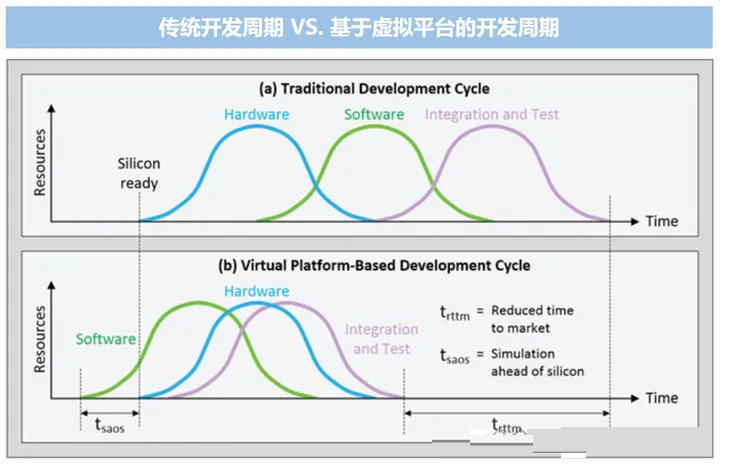

下图为传统产品开发周期和使用Simics虚拟平台的产品开发周期所需的时间和风险的对比。X轴为时间和风险,Y轴为所需的工程资源。从图中可以看出,采用虚拟平台的方式,可以实现软件开发和集成测试的左移,从而降低风险、缩短产品TTM上市时间,降低所需的工程资源的成本,提高产品质量。

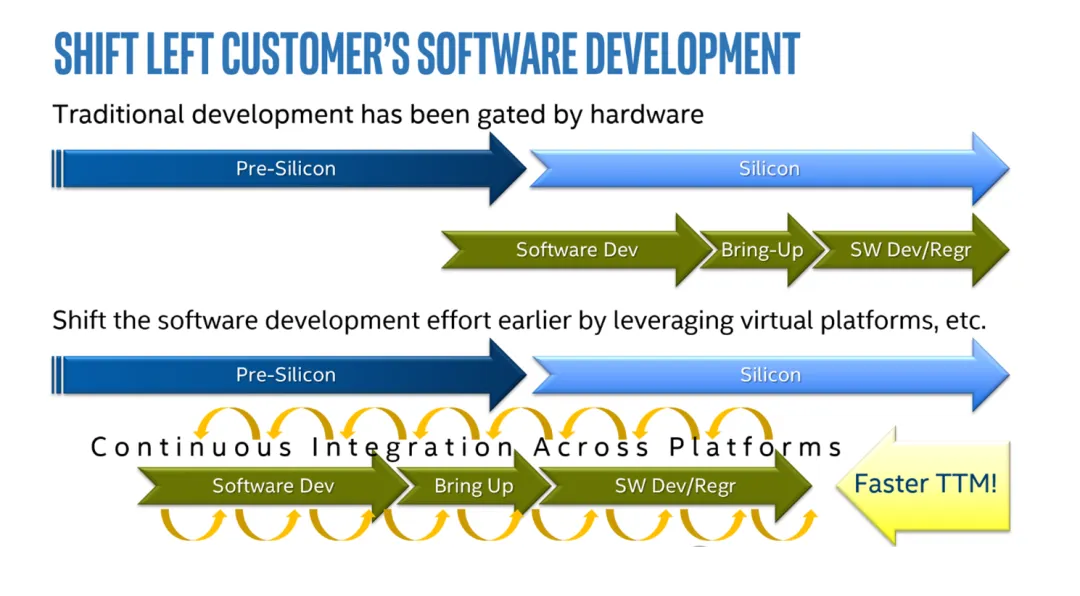

在上图中,采用虚拟硬件平台之后,软件活动可以左移到硬件出来之前,不过画的不是太明显。下图则更清楚地表达了这一点——软件活动从硅后(post-silicon)阶段左移到了硅前(pre-silicon)阶段。

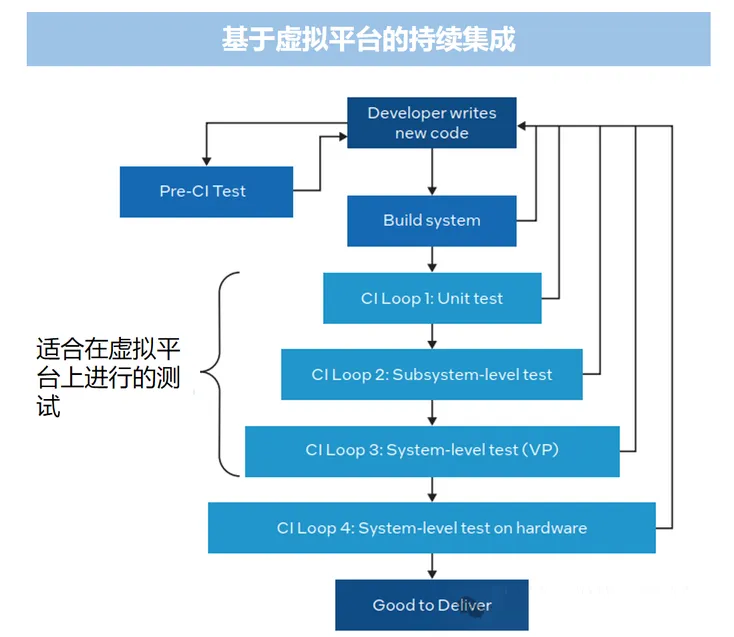

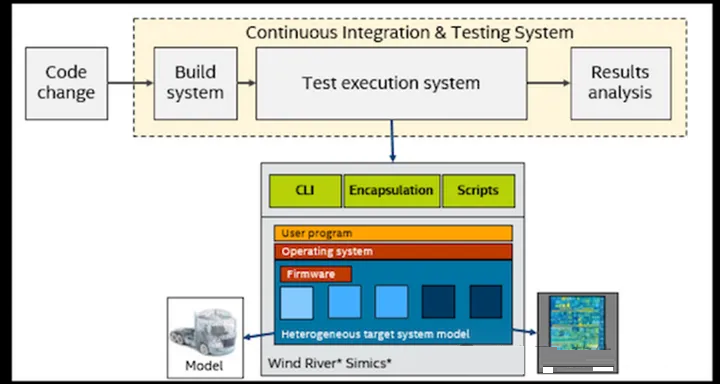

虚拟硬件平台的目的,不是为了替代真实的硬件,而是为了尽早为开发人员提供快速反馈。这样开发人员就可以像软件的持续集成一样,对硬件进行持续集成(CI)。

通过Simics虚拟硬件仿真平台,英特尔可以帮助客户实现软件开发测试的左移,缩短产品的 TTM(上市时间)。

Simics 支持对 FPGA SoC 中的硬核处理器系统(HPS)以及其他组件进行建模和仿真。这些模型包括处理器、内存、I/O设备等,它们共同构成了一个完整的虚拟硬件环境。开发人员可以在这个环境中编写、调试和测试软件,从而大大提前了开发周期。

英特尔Simics支持以下功能:

虚拟原型:Simics 支持 DML 设备建模语言,可以模拟不同的目标硬件环境,为开发人员提供一个虚拟的原型。这使得开发人员可以在没有实际硬件的情况下进行软件开发和测试,从而大大缩短了开发周期。

故障注入:Simics支持故障注入功能,允许开发人员模拟硬件故障并观察软件的行为。这有助于开发人员更好地了解软件的健壮性和容错能力,并提前发现并修复潜在的问题。

协同工作环境:由于Simics完全在PC上运行,因此虚拟平台可以分发给全球的开发团队。这使得多个开发小组可以在同一个虚拟环境中进行协同工作,大大提高了开发效率和吞吐量。

基于 Simics,就可以解耦软硬件的设计开发,实现并行设计开发。例如,波音767的显示单元的软件代码,基于Simics

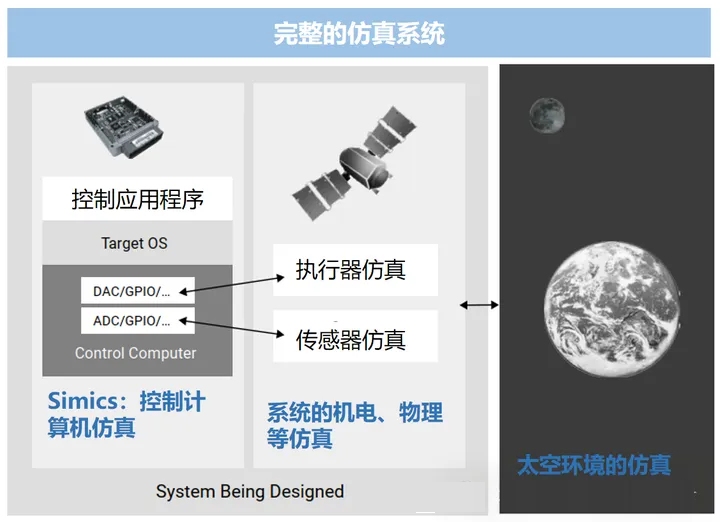

仿真器进行代码覆盖率测试。NASA 利用 Simics 对卫星的安全关键的控制应用程序进行仿真,其中包括基于Simics的控制计算机的仿真,基于多物理仿真软件的机电、物理仿真,以及基于STK的太空环境的仿真。

Windriver也提供基于Simics的综合模块化航电软件的开发测试工具。

Windriver 基于Simics虚拟硬件平台,加上航电相关的软件模块,就可以为航电软件开发提供虚拟硬件平台,从而加速航电软件的开发。

另一个和 Simics 设计理念非常相似的另一个技术,就是英特尔等厂商提供的 ACRN 虚拟化技术。这一技术结合了轻量级

hypervisor 的设计理念,专为嵌入式和物联网场景打造。

4.2 云计算硬件测试评估的左移(微软 Azure)

提出厂商:微软

左移对象:云计算硬件系统的测试评估

左移方式:通过微软开发的虚拟客户端库VC,运行不同硬件的工作负载基准测试软件,分析云上的硬件的实际性能,生成相应的硬件评估报告

左移价值:更快完成云计算数据中心硬件的性能、可靠性和安全性的验证

经常使用云计算服务的读者都知道,云上的硬件资源其实是分代的,比如服务器、网络、训练和推理AI模型所需的显卡等。

在激烈市场竞争环境之下,云计算硬件厂商(其中包括英伟达和AMD等AI算力厂商),会持续发布更新换代的硬件;而像微软Azure云、AWS、谷歌等云服务提供商,就要跟在硬件厂商后面,持续不断在自家的云上测试评估硬件厂商的新一代的硬件,先小规模测试评估,再大规模测试评估,然后再部署。随着为人工智能领域开发的AI硬件平台数量不断增长,对这些硬件系统进行测试评估以用于云生产环境成为一项艰巨的任务。

为了领先竞争对手,云服务提供商就有动力对新一代的硬件测试进行左移,从而缩短新一代硬件更新换代所需的时间,从而为用户提供更先进的云服务。

对于微软的Azure云上的硬件系统,需要在硬件厂商提供的每一代新的硬件系统上,运行许多不同类型的测试。其中有三大测试左移的技术挑战。第一个是确保硬件系统能够按照设计规范运行。第二个是自动化高效地运行不同的行业或厂商提供的性能基准测试(performance

benchmark)程序,以实际测量硬件系统的性能。从而验证实际性能是否和AI算力厂商提供的纸面性能数据一致,更新换代后是否有显著的性能提升。第三个挑战,由于要在每个硬件系统上运行数百个测试项目,所涉及的测试工作量非常大。

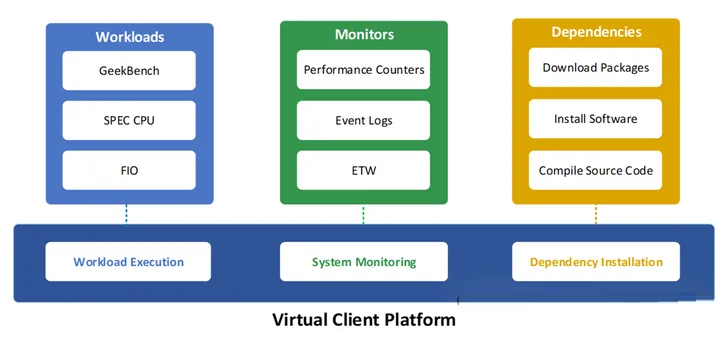

为了解决这三个挑战,微软开发了虚拟客户端(VC)开源项目。它是一个标准化的、协作的、开源的工作负载和行业基准测试平台。它支持40种工作负载(workload)和基准测试(benchmark

test),涵盖 x64 和 ARM64 架构、Windows 和 Linux 操作系统、宿主机和虚拟化运行时。VC

平台可以根据 OCP(开放计算项目,Facebook等创建的开源硬件项目)规范对 OCP 系统(如服务器、网络、存储、固件、冷却等)进行性能、可靠性和安全性基准评估和系统监控。同时它也可以让用户轻松管理所需的依赖软件包。

VC 平台的使用并不局限于选定的几种类型的环境。它可以从单个台式机系统扩展到数据中心的1000个系统。它在较小的应用程序领域(如台式机测试)和可能只有几个服务器节点或几个机架的服务器节点(如早期设计阶段的

SKU 验证)的开发环境中非常有用。它也可以在有大量服务器硬件集群需要验证的场合下运行。

VC 平台最大限度地减少了在裸机环境和虚拟化环境中评估系统的区别,它可以在这两种环境中无缝运行。这非常有价值,因为它让用户可以先在裸机环境中执行初始硬件评估,然后将结果与硬件虚拟化环境中的结果进行对比。在大多数情况下,裸机测试提供了硬件性能的最真实视图,期望达到的最高性能水平。在虚拟化环境中测试生成的结果,则更接近客户体验(商业云生产环境用例)。在虚拟化环境下,由于更复杂的软件技术栈,性能不会像裸机执行那样高。

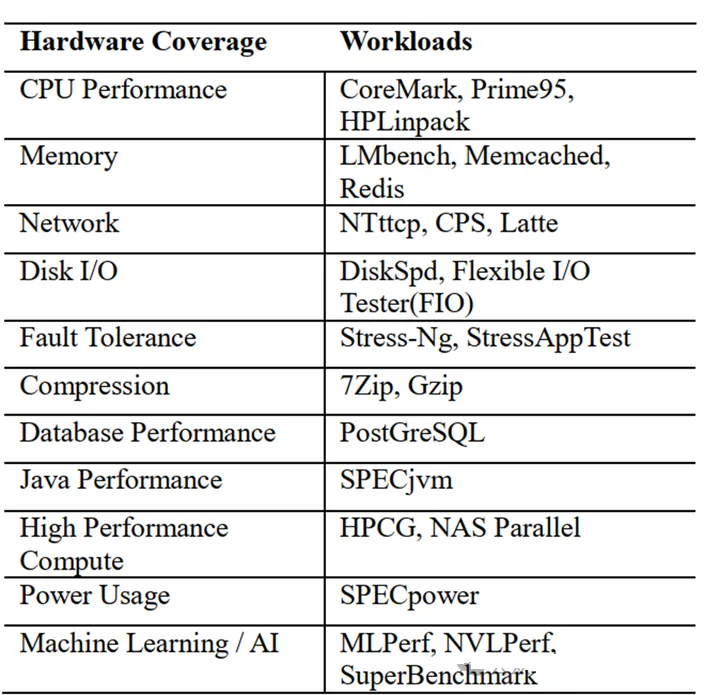

VC 平台为硬件验证和系统性能测量提供了广泛的工作负载。有许多基于Windows/Linux的标准化工作负载可以运行在x86和基于ARM的架构上,从而可以在CPU、内存、网络、磁盘等方面进行全面的测试和性能比较。有几个新的机器学习/人工智能工作负载,如MLPerf和superbenchmark,具有详细的性能指标,允许工程师评估系统之间的训练/推理性能。

下图显示了 VC 平台上当前可用的一些工作负载示例。通过从 VC 中选择工作负载,可以实现对许多硬件领域和用例的覆盖。

VC 测试过程的所有测试数据,都被采集并上传到 Azure Data Explorer(ADX)实时和时间序列分析服务中。通过使用

ADX 支持的 Kusto 查询语言(KQL),用户可以跨不同领域对测试结果进行验证分析(如可靠性、性能、安全性):

工作负载输出数据:了解执行进度和结果。

上下文信息数据:工作负载/测试执行期间的系统状态,这对于识别预期操作条件中的违规行为很有用。

VC执行的单步命令:了解单个工作负载/测试工具集或平台运行时本身是否存在故障。

VC 也支持对AI算力硬件的测试。微软系统工程团队和 VC 工程团队合作,就可以快速方便地验证Azure云上的

Nvidia 和 AMD 集成 GPU 的 AI/ML 服务器平台:

Nvidia H100 PCIe 显卡(高性能的GPU芯片,专为AI优化,特别是在训练和推理大型和复杂的机器学习模型方面表现出色)和NVIDIA

HGX H100 平台(用于AI 和 HPC的高性能计算平台)的工作负载:SuperBenchmark、GPU

Stream、Nvidia DCGMI。

AMD Radeon Pro V620 显卡(面向云端用户的现代办公、3A游戏、3D内容创作等需求)的工作负载:Furmark、SGEMM、UBM

Perf。

4.3 高速 PCB 电路板设计的测试左移(Cadence)

提出厂商:Cadence

左移对象:PCB 电路板设计

左移方式:通过基于IBIS和DML的电路板级仿真,提前发现电路设计缺陷

左移价值:缩短PCB设计调试时间,提高产品可靠性

随着集成电路的速度不断提高,电路的复杂性不断增加,信号完整性(SI)、电源完整性(PI)和电磁兼容性(EMC)等,就成为了高速

PCB 板级设计必须考虑的问题。

为了在当今竞争激烈的电子市场上取得成功,“左移”正变得越来越流行。它的作用是在设计过程/工作流程的早期发现并防止缺陷,通过在生命周期的早期将工程任务移到左边来改进电子产品和系统的质量和性能。

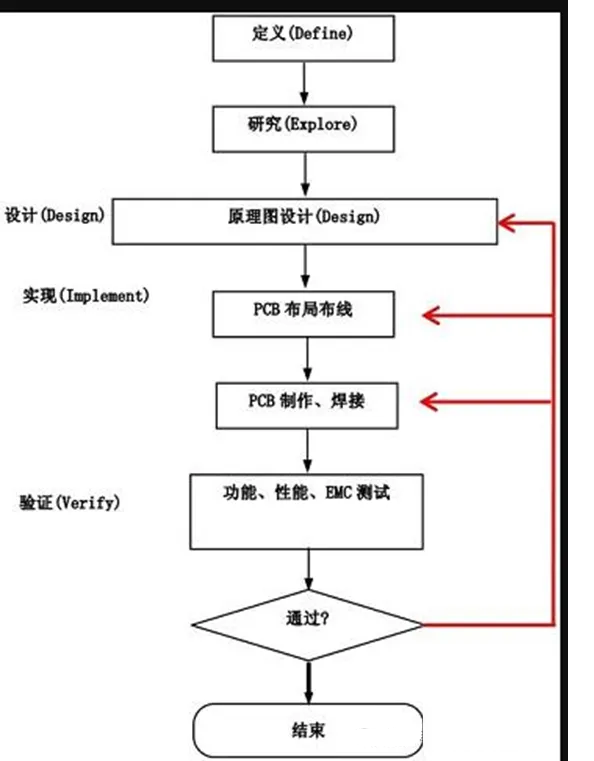

传统的高速 PCB 电路板的设计流程如下图所示。

这种传统的设计流程本质上是顺序的(sequential,或线性的)——硬件工程师先基于经验进行设计原理图和Layout,然后根据设计找

STM 代工厂生产 PBC 电路板的原型样机,再然后对样机进行调试和测试,如果测试发现问题,再修改设计并重新生产测试。

上述过程经常需要经过多次的重复。这在当前激烈的市场竞争面前,无论是在设计时间、设计成本还是设计的复杂程度上都无法满足要求。

解决办法就是 PCB 设计测试的左移,通过电路板级的虚拟仿真,在生产出电路板之前,就通过电路仿真发现原理图设计和

Layout 设计中存在的问题。

对于电路板的信号完整性、电源完整性要求,就要基于信号完整性进行PCB仿真设计。仿真模型通过对信号完整性的计算分析,得出设计的解空间,然后在此基础上完善优化

PCB 设计,最后再验证当前设计是否满足预计的信号完整性要求。如果不能满足要求,可以根据各个设计环节的设计点和检验机制,迅速定位问题和找到根因。

加入了上述仿真设计的 Cadence 高速电路设计的设计流程,如下图所示。

与传统的顺序的 PCB 板的设计相比,这种新的高速电路的设计流程具有如下优点:

将大量的原型样机的调试工作, 提前到设计阶段, 增强了调试阶段的时间可控性;

增强了各个阶段设计正确性的可控性, 对可能出现的设计问题进行定性和定量的分析;

缩短整个产品开发调试周期, 节约开发成本;

提高产品的可靠性、一致性和复用性。

这种左移后的新的设计流程的特点是:

以 IBIS 模型为基本出发点;

以高速信号的仿真分析为手段;

以规则驱动为系统设计的质量保证。

英特尔等厂商联合提出了 IBIS 标准,用于对有源器件进行建模。这种模型是一种黑箱模型,提供了电子器件的关键信息,可以在保护器件提供商的IP知识产权的同时,用于对电路进行整体的仿真。

IBIS 模型提供电路元器件的行为描述,但不泄漏电路内部构造的知识产权细节。换句话说,销售商可以用IBIS模型来说明它们最新的门级设计工作成果,而不会给其竞争对手透露过多的产品信息。也正因为如此,本质上讲,IBIS

模型并不能叫做一种“模型”,它只是描述器件行为的数据文件。

虽然IBIS模型已经是业界描述有源器件的一种标准,但是对于系统仿真而言,不仅仅需要关注于有源器件模型,还需要增加对离散器件、接插件、电缆及系统之间的互连模型。只有这样才能有效地描述一个系统,从而对系统的整体性能进行仿真。为了支持这种需求,Cadence开发了DML语言,用于对所有类型的器件模型进行描述和封装,从而使得一个系统能够在一个统一的环境下进行仿真。

4.4 RTL 设计的左移(瑞萨)

提出厂商:瑞萨(日立SoC、三菱SoC、NEC SoC 三家合并)

左移对象:RTL 数字前端测试

左移方式:通过将测试左移到综合之前,提前发现 RTL 设计缺陷

左移价值:缩短设计调试时间,提高产品可靠性

传统的RTL数字前端设计,是在综合之后进行 DFT 测试验证。这种方式费时费力,还要经常返工。

通过将 ISTC、IJTAG、MBIST、EDT、LBIST 等测试左移到综合左边,可以提前发现安全问题,从而降低

TAT 周期。

这里面的关于内建自测试、扫描链、压缩算法之类的测试细节,过于专业,就不解释了,具体请参考相应的材料,比如《数字集成电路测试:理论、方法与实践》一书。

当然,上面的这个瑞萨的测试左移的案例,是瑞萨作为 EDA 工具提供商提供的测试左移的工具。

对于硬件设计厂商的芯片测试左移,则有诺基亚的 5G 数字前端的左移的案例。不过这个案例的左移,更偏向于在硬件之上的

Matlab 算法代码生成与硬件结合的思路。

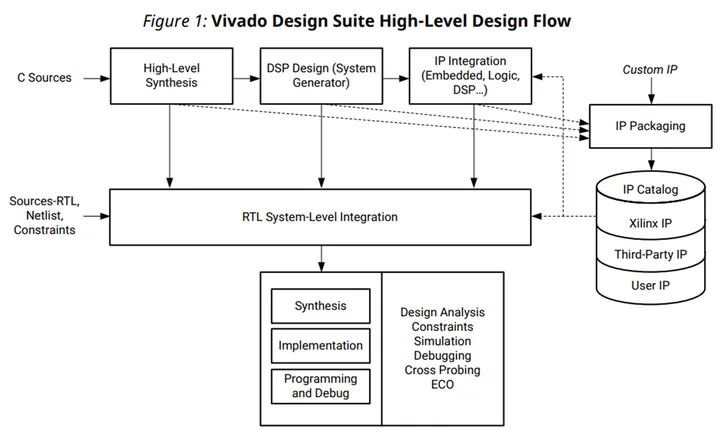

4.5 FPGA 和 SoC HLS 设计测试的左移(Xilinx)

提出厂商:Xilinx

左移对象:FPGA 和 SoC HLS 设计测试

左移方式:通过数据模型对全可编程器件进行仿真和测试,并复用 IP

左移价值:缩短 FPGA 设计调试时间,提高产品可靠性

赛灵思(Xilinx)的 Vivado 和 Vitis 都是其针对 FPGA(现场可编程门阵列)和SoC(系统级芯片)开发的重要软件工具,但它们在功能、用途和定位上有所不同。

Xilinx 主打全可编程(All Programmable)器件,Vivado 设计套件正是 Xilinx

在这一趋势下精心打造的可编程逻辑开发环境。Vivado设计套件包括高度集成的设计环境和新一代IC级的设计工具,这些均建立在共享的可扩展数据模型和通用调试环境基础上。

Vivado 是一款集成开发环境(IDE),主要用于FPGA和SoC的设计与开发。它提供了从系统到IC级的全方位设计支持,包括快速综合和验证C语言算法IP的ESL设计、标准算法和RTL

IP封装技术、模块和系统验证的仿真速度提升、硬件协仿真性能优化等。

Vivado 设计套件的所有功能,都是基于一个共享的可扩展的数据模型构建的。它的出现使得 Xilinx

全可编程器件的整体性能得到了很大的提升。

Vivado 设计套件采用快速综合和ESL设计,实现重用的标准算法和RTL封装技术,模块和系统验证的仿真速度提高了3倍。

Vivado 设计套件采用层次化器件编辑器和布局管理器,速度提升3~15倍;为业界提供最好支持的

VHDL 逻辑综合工具,速度提高4倍;使用增量式的工程变更管理,加速设计修改后综合和实现的快速处理。

下图为 Vivado 的设计套件的设计流程。

Vivado 更侧重于硬件设计和开发,提供了全面的硬件设计工具和仿真环境。Vitis 则更侧重于软件和算法的开发,以及硬件加速的实现。两者相互补充,共同构成了

Xilinx 完整的 FPGA 和 SoC 开发解决方案。

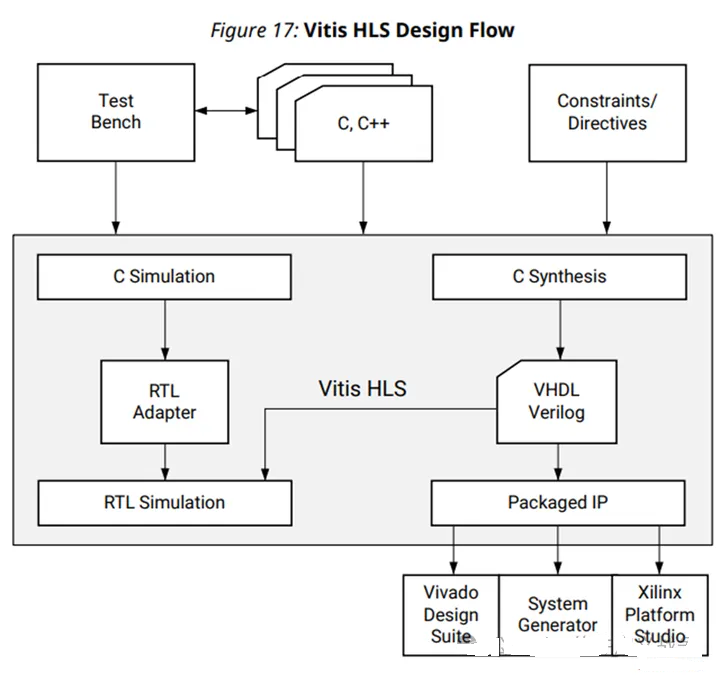

而 Vitis 是一款统一软件平台,简化 FPGA 和 SoC 的开发流程,提高开发效率。提供了丰富的加速库和API,支持高效的硬件加速,广泛应用于AI推理、信号处理、视频处理等领域。

Xilinx 的 Vitis HLS 设计流程分为五个步骤(见下图)。

编译、模拟和调试 C/ c++算法。

查看报告,分析和优化设计。

将C算法综合到 RTL 设计中。

使用 RTL 联合仿真验证 RTL 实现。

将 RTL 实现打包为编译后的对象文件(.xo)扩展名文件,或者导出为 RTL IP。

从这两个设计套件的设计流程,我们可以看出有三种左移:

开发者只需要用C/C++等高级语言编写代码,无需编写底层的VHDL、Verilog代码;

通过设计套件提供的 Test Bench 测试工具,在设计阶段就可以进行 RTL 仿真测试和验证;

通过提供的IP核以及加速库和API,可以让开发人员减少开发工作量。

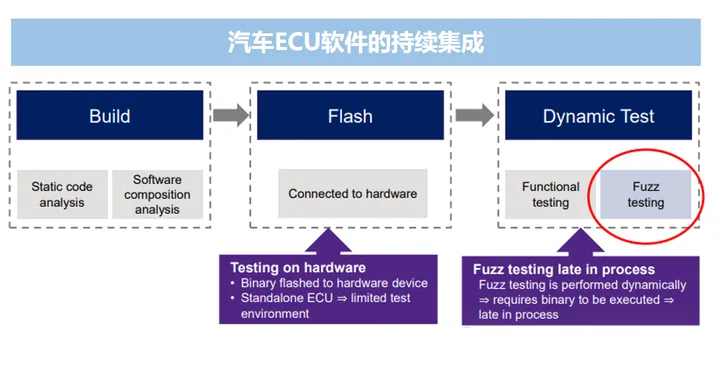

4.6 汽车 ECU 软硬件开发测试的左移(Synopsys)

提出厂商:Synopsys

左移对象:汽车ECU SoC设计、ECU软件的测试

左移方式:汽车专用IP、虚拟硬件平台上的仿真和测试、自动化汽车软件测试套件

左移价值:缩短设计测试时间,提高汽车安全性,减少汽车召回

未来十年,为了适应大数据和自动驾驶等大趋势,汽车行业在开发过程中正在经历一次重大变革。汽车预计将需要10亿行代码的支持,而当前的汽车则有1亿行代码。预计软件和电子产品将占汽车创新的90%,软件可控制一切,从安全关键系统(如刹车和动力转向),到基本的车辆控制(如门窗、V2V、V2I),以及复杂的信息娱乐系统和远程信息处理。

但是,随着软件数量呈指数级增长,软件缺陷也会急剧增加。普通汽车预计将包含多达15万个错误,其中许多错误可能会损害品牌以及客户的满意度,并在最极端的情况下导致灾难性故障。

Synopsys(新思科技)的汽车电子软硬件的左移方案,包括了三种左移:

更智能、更安全的汽车SoC设计

并行软件和硬件开发

早期和全面的汽车软件测试

这三种左移结合在一起,将传统的顺序的 V 模型的汽车开发过程,转变为并行的过程。它使设计师能够在设计过程中更早发现错误,更便宜地修复错误,而且可以通过虚拟模型看到前期设计。

采用“左移”策略,设计团队可以从一开始就将功能安全性和可靠性融入到SoC中;在硬件可用之前,提前18个月开始软件开发并识别问题;并在开发和测试期间以及在整个供应链中构建安全性和质量。

第一种左移:更智能、更安全的汽车SoC设计:使用汽车专用IP构建块在硅上实现专用功能

与从零开始相比,SoC设计师通过重用预先设计、预先验证、可重用的构建块(IP核)的。Synopsys

DesignWare 汽车 IP 包括符合 ISO 26262 标准的逻辑、接口、安全岛和具有嵌入式视觉、神经网络和传感器融合功能的处理器。它保证了不同级别的

ASIL (A、B、C和D)合规性,并符合严格的 AEC-Q100 可靠性标准。

采用 Synopsys 汽车 IP 可加速 ADAS、信息娱乐和 MCU 设计开发。有了它,设计人员可以在硅上构建专用功能,降低集成风险,并从一开始就将功能安全性和可靠性设计到

SoC 中。

第二种左移:并行软件和硬件开发:利用仿真和共享模型在虚拟平台上早期开发软件

传统的汽车开发流程是串行的——先开发 ECU,然后开发软件。并行开发意味着可以在开发 ECU 的同时开发虚拟原型,因此可以在硬件可用之前很久开始软件开发,软件开发可以提前18个月启动。

虚拟原型还促进了整个汽车供应链的协作,帮助定义芯片架构,最终提高结果质量并缩短生产时间。

第三种左移:早期和全面的汽车软件测试:增加覆盖率,加速测试周期,并使用自动回归来允许频繁的软件更新

Synopsys 进一步利用虚拟模型,帮助客户创建虚拟汽车开发的测试平台。通过静态安全测试、软件组合分析、交互式安全测试和模糊测试,对安全关键的

ECU 软件进行广泛的验证。

Synopsys 帮助客户在其汽车软件生命周期中构建安全性、质量和合规性——从开发到测试再到无线更新。还可以检测第三方组件、安全漏洞、许可证使用和代码弱点。帮助企业与

ISO 26262、MISRA 和其他新兴网络安全标准保持一致。

除了上述的三个左移,Synopsys 还有一个用于低功耗芯片验证的左移,即通过分层的 SAM(抽象

Signoff 模型)平衡验证的性能和准确性,从而大大缩短低功耗芯片验证(Signoff)所需的时间。

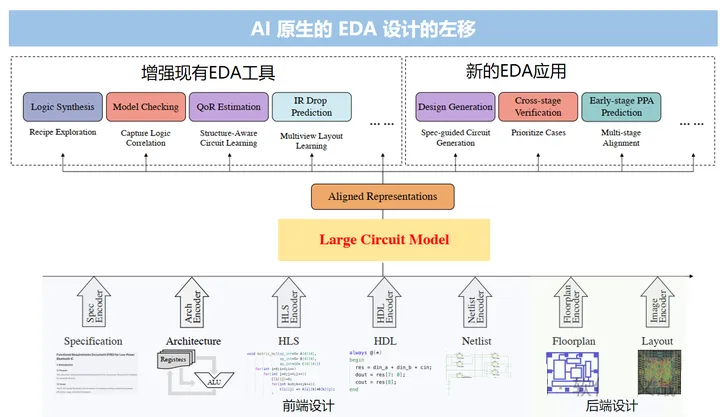

4.7 多模态EDA大语言模型 (香港中文大学、北大、东南大学、华为诺亚方舟实验室等)

提出厂商:香港中文大学、北大、东南大学、华为、宁波大学、香港理工大学、鹏城实验室、上交、复旦

左移对象:EDA 芯片设计

左移方式:通过构建跨整个EDA流程的 EDA 领域专用的多模态大语言模型 LCM,增强现有的 EDA

工具,以及生成新的 EDA 应用

左移价值:简化 EDA 流程,缩短上市时间,并从不同抽象层次的整体上优化芯片的 PPA

通常我们用的大语言模型是单模态的,主要处理的是文本信息,经过训练的大语言模型可以理解文本的语义信息。但是现在也有多模态大语言模型(Multimodal

Large Language Model, MLLM)了,它处理的模态有多种,包括文字、图像、音频、视频等内容。

多模态大语言模型的基本原理是将文本、图像、音频等多种模态的数据进行融合,并训练一个统一的模型来处理这些数据。这种模型能够学习到各个模态之间的关联性和互补性,从而实现跨模态的语义理解和生成。

多模态大语言模型通常采用 Transformer 架构,并通过多模态编码器(Multimodal

Encoder)来处理不同模态的数据,将其表示为向量嵌入。然后将不同模态的向量嵌入进行模态对齐,将它们对齐到一个语义空间中。最后通过

虽然多模态模型可以具有各种架构,但大多数多模态框架都包含以下元素:

编码器:此组件将不同类型的数据转换为机器可读的向量嵌入。多模态模型通常为每种数据类型(无论是图像、文本还是音频)配备一个编码器。

融合机制:此机制将所有不同的模态组合在一起,以便模型能够理解更广泛的上下文。

解码器:最后,还有一个解码器,它通过解析来自不同类型数据的特征向量来生成输出。

面向文本的单模态的大语言模型要喂给它大量文本数据进行训练。支持文本、图像、音视频的多模态大语言模型也不例外,它的训练过程如下:

数据准备:多模态大语言模型需要大量的多模态数据来进行训练,包括文本、图像、音频等。这些数据应该足够多样化和丰富,以覆盖模型需要处理的各种情况。

训练策略:训练多模态大语言模型需要采用合理的训练策略,如联合训练、分阶段训练等。这些策略有助于模型更好地学习到不同模态之间的关联性和互补性。

视觉-语言对齐预训练:在训练过程中,通常利用大规模“图像-文本对”(简称图文对)进行端到端训练,进而对齐两种不同的语义空间。由于视觉模型和语言模型之间存在较大的语义空间差异,因此这一步骤对于实现跨模态的理解和生成至关重要。

视觉指令微调:在视觉-语言对齐预训练之后,可能还需要进行视觉指令微调。这一阶段通常收集一些高质量的详细图片描述,并将其组织成对话形式进行模型微调,以提高模型的语言流畅度和对话交互能力。

借鉴多模态 LLM 的思路,可以为数字电路创建专门的多模态的大语言基础模型。这个基础模型被命名为

LCM 大电路模型。只不过这里的多模态指的是 EDA 设计流程中的 Spec、架构、HLS、HDL、网表、Floorplan、Layout对应的文本或代码,而不再是文本图像或者音视频。

这样做是非常可行的,因为我们都知道,EDA行业是高度软件化的,表面上是电路设计,实际上是不同抽象综合层级的代码。所以这个LCM的思路,本质上就和训练代码生成的大语言模型非常类似。

具体来说,EDA 两大流程前端设计和后端设计看做一个统一的 EDA 设计连续统。在这个 EDA 设计连续统的每个设计阶段的设计工件,都看做是一个单独的模态。通过对每个设计阶段的设计工件(比如HLS、HDL代码),通过多模态编码器来处理不同模态的数据,然后对齐。

AI4EDA 方法无法实现整体设计的综合和理解,因为其忽略了电路数据的电气、逻辑和物理方面的复杂相互作用。主张从

AI4EDA 到 AI 原生的 EDA 的范式转变,将AI集成到设计过程的核心。实现这一愿景的关键是通过协调和提取各种

EDA 流程上的数据源(如功能规范、RTL设计、电路网表和物理布局),开发一种多模态的电路表示技术,从而提供全面的理解。

通过 LCM 这一 EDA 领域的基础模型,就可以在整个 EDA 设计连续统中,融合和对齐不同设计阶段的不同模态的设计工件,从而创建出从高级功能规范到详细物理布局的统一描述。然后基于这个训练好的多模态大语言模型,就可以用于增强现有的

EDA 工具,或者开发新的 EDA 应用。这种统一的方法,可以简化 EDA 流程,缩短上市时间,并从不同抽象层级的总体高度优化芯片的

PPA(功耗、性能、面积)。

LCM 模型本质上是多模态的,编码和解码电路数据的丰富语义和结构,从而培育出更具弹性,高效和创造性的设计方法。拥抱这种

AI 原生的 EDA 设计哲学,就可以预见到一个超越当前 EDA 工具的发展路径,点燃电子设计方法论的深刻“左移”。

这种方式不仅预示着现有 EDA 工具的演变,而且预示着一场革命,有望从根本上提高 EDA 设计生产力,开创一个新的时代。在这个未来的新时代,电路性能、功率和面积(PPA)的优化不是逐步实现的,而是利用大语言模型辅助电子设计自动化,打破现有

EDA 工具链的多阶段独立优化的壁垒,实现全流程辅助设计,实现真正的跨阶段设计、跨器件、跨工艺的全局协同优化。

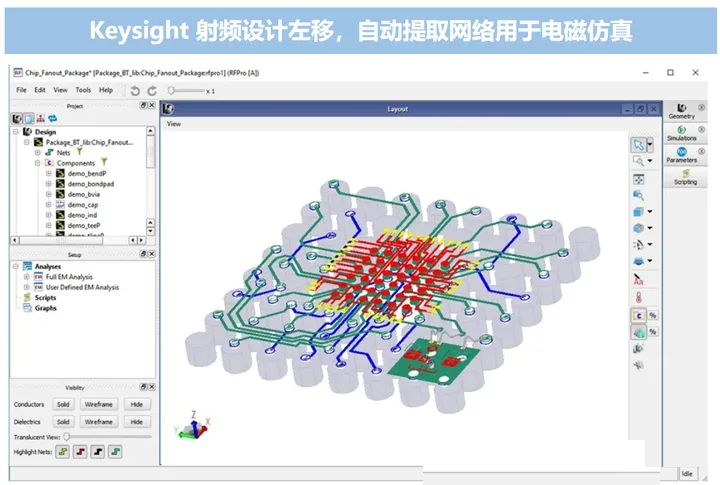

4.8 射频设计的左移(Keysight)

提出厂商:Keysight

左移对象:RF 射频设计

左移方式:在构建物理原型之前,通过虚拟原型和建模仿真,实现提前进行射频电路的设计验证

左移价值:缩短产品上市时间

Keysight 推出Keysight EDA 2024,这是一套紧密集成的电子设计自动化(EDA)软件工具。这种新的集成EDA软件有助于“左移”,以提高射频工程师在多种应用中开发高速、高频产品的生产力。

Keysight 的左移是一种射频领域的工程实践,它将设计验证在开发周期中向前推进,以加快上市时间。电子系统日益复杂,要求设计人员在虚拟领域完成尽可能多的验证,因为在虚拟领域更容易、更经济地纠正功能和物理问题。虚拟原型和数字孪生的精确建模和仿真方法,对于处理电子系统的复杂性至关重要。

Keysight EDA 2024 软件包括新的系统和电路设计工作流集成、功率放大器建模和仿真优化以及卫星通信设计演进增强。这一新工具提供了一个全面的解决方案,让工程师在构建物理原型和开始批量生产制造之前,通过高度精确的验证加速虚拟原型的创建。

Keysight EDA 2024软件套件提供以下左移能力:

RF 系统资源管理器,简化了系统和电路级设计工作流程,便于对系统架构进行早期探索。

数字预失真管理器和数字预失真设计器,使用动态增益模型,加速宽带隙功率放大器的设计和验证。

SystemVue 为 5G 非地面网络、DVB-S2X 和相控阵产品开发,提供完整的卫星通信建模和仿真解决方案。

1. 简化系统和电路设计工作流程

RF 系统资源管理器将系统架构探索和分析功能,从 SystemVue 集成到高级设计系统(ADS)中,以实现系统和电路级工作流之间的设计共享。RF

System Explorer 为电路设计人员分配一个分层子系统和参数,以更改射频(RF)块参数或选择分析路径,而不会影响整体架构。电路设计人员可以将他们的电路设计或派生的行为模型合并到分配的子系统中进行射频验证和优化。

SystemVue 和 ADS 之间的协同工作流,使设计人员能够提取电路设计的模型,并使用 RF

系统资源管理器进行仿真。这个顺畅的工作流程,为开发团队中的架构师和子系统工程师带来了更有效的沟通。系统架构师在SystemVue

中预先配置他们自己的模板,以便与 RF 电路设计团队更有效地协作。工程团队还可以避免在 ADS 中重复显示结果。

2. 优化宽带隙功率放大器的建模与仿真

与 RF System Explorer 的工作流集成一样,数字预失真(DPD) Explorer和

DPD Designer 工具可以跨抽象层次优化功率放大器设计方法。这些工具使致力于宽带应用(包括5G

FR2、DVB-S2X和WLAN)的功率放大器设计人员能够利用新的动态增益模型。

紧凑的波形提供了无与伦比的仿真速度和 DPD 优化,改善了整个功率放大器的设计和验证过程。DPD

Explorer和 DPD Designer 采用与是 Keysight PNA-X 相同的精确测量科学和算法,确保相邻通道功率比(ACPR)和误差矢量幅度(EVM)指标的高性能结果。

3. 演进的 5GNTN、DVB-S2X 和相控阵应用卫星通信设计

SystemVue 增强功能可解决5G非地面网络(NTN)、DVB-S2X 和相控阵开发项目。

对于 5G NTN, SystemVue使用 3GPP Release 17 的1024 QAM

调制和相关的 MCS 表更新了 5G NR 仿真库。该库支持各种 NTN 部署的完整端到端物理层系统仿真、新的

5G 信道模型和先进的收发器。NTN 的信道模型提供了模拟各种卫星链路的所有传播特性。

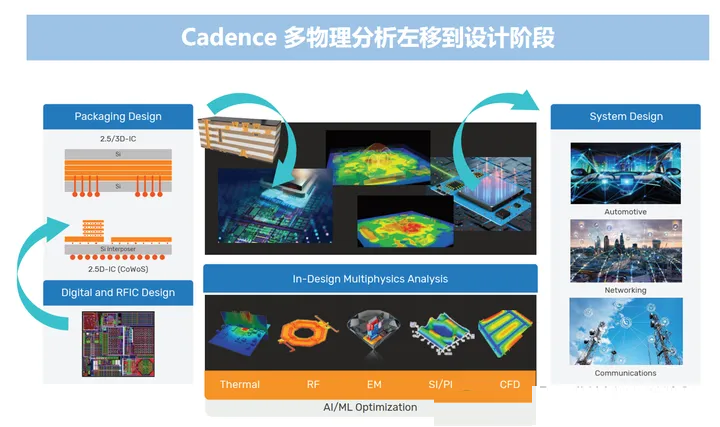

4.9 多物理场仿真(Cadence)

提出厂商:Cadence

左移对象:多物理场仿真

左移方式:在构建物理原型之前,通过虚拟原型和建模仿真,进行多物理场仿真和分析验证

左移价值:提供了前所未有的工程效率,更快地将更高质量的产品推向市场,提高了性能和产量,缩短了设计周期,降低了风险。

在电子设计自动化(EDA)领域,多物理场分析也要一起左移,从而成为芯片、封装、电路板和整个系统级设计过程中每个阶段不可或缺的一部分。

Cadence 不仅包括 IC、PCB和IC封装设计平台,还包括多物理场设计。多物理场设计分析工具,包括信号完整性/功率完整性(SI/PI)、电磁(EM)、热力学和计算流体力学(CFD),以及射频/微波效应。

Cadence 的多物理场系统分析解决方案,为工程师提供了无缝的工作流程,加快了周转时间(TAT),同时使工程师能够保持在相同的环境中,无需集成外部供应商的多物理仿真工具,从而最大限度地降低了风险。

4.10 电子产品生产测试的左移

电子产品测试的左移,有两个案例。一个是电子代工厂的生产测试的左移,一个是芯片制造厂Fab生产测试的左移。

案例一:电子代工厂的生产测试的左移

提出厂商:富士康、捷普等电子产品代工厂,苹果也有(让给它生产的代工厂用)

左移对象:电子产品产线测试

左移方式:在产线正式生产之前甲方产品工程设计阶段,代工厂测试团队同步对被测设备(DUT)进行测试计划、测试设计和测试夹具设计、测试代码编写

左移价值:通过产线测试左移,缩短产品上市时间,提高生产良率和Cpk

除了在设计阶段需要测试左移,通过仿真及早发现并解决 PCB 电路板的设计问题外,对于一些头部的电子代工厂来说,尤其是在生产重要产品时,电子代工厂的测试部门,也需要左移——提前根据客户提供的硬件设计规格等资料,制定相应的测试计划、设计测试方案和测试夹具、编写测试脚本/测试设备协议驱动等。

和 EDA 领域一样,也会有相应的测试工具(Test bench),其架构设计理念和 UVM 之类的芯片测试平台很相似。

通过测试脚本,测试工程师可以与如下测试设备和系统交互:

电源

示波器,网络分析仪和频谱分析仪

万用表、电表等

DAQ卡,PXI和VXI仪器

JTAG控制器,EEPROM编程器等

计算机视觉检测系统

MES系统

......

案例二:芯片制造厂 FAB 的生产测试的左移

提出厂商:西门子

左移对象:半导体 Fab 生产测试

左移方式:在芯片产品生命周期的早期推动产品验证和制造验证

左移价值:减少后期昂贵的变更

西门子的半导体生产数字化解决方案包括三个核心概念:

数字孪生:在物理世界中发生的实际过程、产品或服务的虚拟模型

数字主线:在企业中编织在一起的多个数字孪生

左移:在产品生命周期的早期推动生产和工艺的虚拟验证,以减少后期昂贵的变更

5. 总结

对于软件定义战争来说,左移和连续统、测试评估,这三者的共同之处在于,它们都是被大大低估但是非常重要的研究对象。它们实际上是理解任务工程、数字工程、敏捷、任务工程、系统工程、软件工厂、DevOps、DevSecOps、CI/CD、ModDevOps、DevNetOps、DevWarOps、DevStar(Dev*)、MOSA

GRA 等主题的重要切入点。同时左移也是理解作战能力连续统、测试评估连续统的关键。所以花这么多时间打窝,也是值得的。

说来惭愧,由于我是学变化之学出身的,软件当年是靠《24小时学会系统安装和重装》、《21天学废 C++/Java》入门的;硬件虽然见过别人画原理图和

Layout,也参观过 SMT 贴片厂和 Fab,但是实际上只见过猪跑没吃过猪肉。所以本文花了两周时间,期间写的十分痛苦,不过也学到了不少东西。

本文在介绍硬件的左移案例时,相关的技术细节不会讲太多。一方面是因为我自己也不懂技术怕露怯;另一方面是不希望陷入太多的技术细节,以免读者看不清楚左移背后的思想。

不过,为了方便感兴趣的读者,我还是对里面涉及的技术分了大类:

虚拟化技术:Simics 硬件虚拟化、OCP 云资源虚拟化

建模技术:英特尔 DML,IBIS,Cadence DML,Synopsys 低功耗分层 SAM等

仿真技术:射频仿真,SI/PI/EMC仿真,多物理仿真、Keysight 功放增益模型/卫星链路传播模型等

综合技术:EDA 综合设计

芯片测试技术:扫描链压缩,ATE,覆盖测试,模糊测试...

AI/ML技术:多模态大语言模型、基于机器学习的芯片功耗 RCA 根因分析

本文主要面向的不同类别读者,在读完本文后,会有如下收获:

总体部门:了解正在发生的左移的整体态势,了解CPS系统的硬件、软件、测试评估、需求各方之间如何通过数字化手段进行协作;EDA设计作为复杂体系设计其左移面临的挑战有哪些,如何解决,及其对装备体系的左移的启示

系统工程师:了解需求规格、软件、硬件、建模仿真、测试评估之间如何在数字空间中进行并行工程;了解测试评估的最新进展,以便系统工程数字化转型和测试评估数字化转型两者的融合;

试验鉴定:可以举一反三,借鉴用于作战测试评估(OT&E)中,如何为军方用户和采办项目经理提供快速可行动的反馈,联合全域作战下的靶场虚拟化;

纯软件设计开发测试大佬:明白硬件、软件、测试、需求规格如何解耦如何通过虚拟硬件进行协作;知道硬件从RTL到芯片到系统,都可以用软件来表征、设计、仿真、分析和测试;了解硬件与软件如何基于建模仿真实现DevOps的自动化CI/CD流水线;了解硬件如何通过软件建模的思路;被测对象如何提高质量、确保安全(safety)/可靠性等;软件活动如何左移到生命周期左侧与硬件并行工程;如何在前期及早发现软件、架构的可靠性、实时性、稳定性、安全性的缺陷;

纯硬件设计开发测试大佬:硬件设计如何基于硬件设计规格在虚拟平台和测试工具(Testbench)的协助下与软件开发和测试同事协作;如何在软件定义的虚拟硬件平台之上,通过对虚拟硬件的建模和仿真及分析,实现硬件的设计空间权衡探索;如何通过与软件及测试同事的协作,在前期发现硬件设计的缺陷;

软硬两只手都硬的巨佬:以上软件和硬件两者;

EDA 工具研究人员:可以和那篇 EDA LCM 的论文以及北大的那篇 EDA 左移的论文对照看看,互补下。

读完本文的读者,可以结合每个实际案例的具体场景,思考如下概念或理念:“虚拟硬件平台”、“基于模型的虚拟平台”、“基于模型的仿真”、“快速失败、快速学习”、“在设计规格、硬件、软件、测试之间保持一致性”、“CPS

赛博物理系统的 DevOps”、“硬件的 CI/CD 流水线”。

认真思考完之后,您就可以对之前介绍的测试评估连续统的“快速、可行动的反馈”、“可行动的知识”、“Vee

模型的坍缩”有更深刻的理解。

附录A:工控软硬件开发的左移

工控领域的软件开发,是工控领域软硬件协同的编程。这个领域的左移,工具成熟度比软件行业更高,完成的也更早,以至于大家都不认为是左移了。

工控编程左移的历史,其实比软件行业的软件测试左移早得多。这种左移,将原本需要和底层的工控硬件耦合才能完成的工作,通过更高层的领域专用语言的编程,就可以轻松完成。

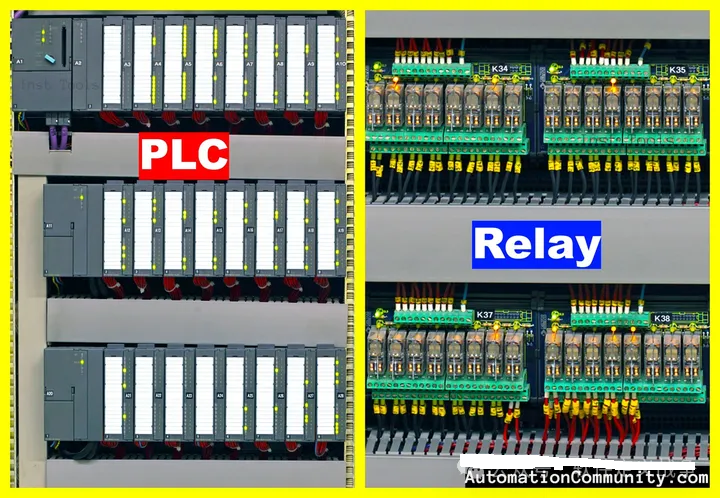

工控左移的典型的例子还有 NC 数控(G代码编程)、PLC 可编程逻辑控制器(梯形图编程等)、Labview(图形化编程)、ROS()、机器人运动控制编程(ABB、库卡等机器人编程语言)、3D

打印的编程(3D切片转数控的G代码)、SCADA(图形化工控组态)。

MIT 和美国空军在20世纪四五十年代发明的 NC 数控技术,通过数控编程,实现对机床刀具运动的控制。

另一个典型的例子是 PLC 的发明,将工控编程从物理的基于继电器的笨拙的编程方式,变为了虚拟的软件编程和调试,最后再通过

PLC 的 I/O 模块的数字量和模拟量接口连接到传感器和执行器进行感知和控制。

|