| 编辑推荐: |

本文主要介绍Infineon Aurix2G TC3XX系列芯片EVADC模块硬件原理,以及MCAL相关配置,和部分代码示例,希望对你的学习有帮助。

本文来自于TechLink汽车软件,由火龙果软件Alice编辑,推荐。 |

|

1 模块介绍

对于汽车芯片来说,模数转换(Analog Digital Conversion,ADC)是一个必不可少的功能,无论是功能安全的电压监控,还是板载传感器的信号交互,都离不开ADC模块。

Infineon Aurix2G TC3XX中有两个ADC模块,一个是 DSADC ,该模块转换速度快,主要为了配合旋变控制器进行电机控制;另一个就是本文要介绍的增强型多功能模数转换器 (Enhanced Versatile Analog-to-Digital Converter,EVADC) ,采用 逐次逼近式转换原理 进行模数转换。

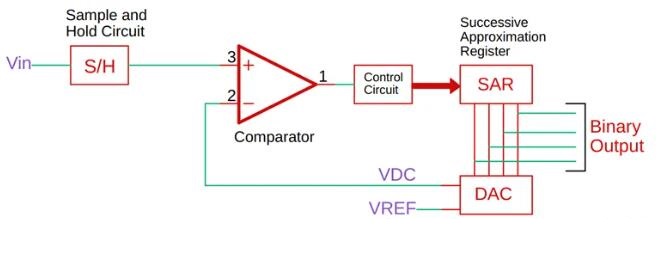

所谓逐次逼近式转换,就是采用逐次逼近转换寄存器 (Successive Approximation Register,SAR) 来实现的,当开始采样时,将SAR寄存器的最高位置1,其余位清零,并由 DAC(Digital-Analog Converter) 输出与该值匹配的电压,与输入电压进行比较,如果输入电压大于该电压,则保留最高位,否则最高位清零;然后从次高位依次向最低位,循环这个反馈调节,直到最低位比较完毕,此时得到的SAR寄存器值就是采样值。我们假设SAR的位宽为N,此时的电压值为 Vin=VREF*SAR/2^N ,采样误差为 Verr=VREF/2^N 。位宽越高则精度越高,但同时也意味着转换时间越长。

(图片来源:https://m.elecfans.com/article/1858599.html)

2 功能介绍

2.1 模块总览

EVADC模块内部有多个 硬件转换单元 ,每个单元都包含采样、转换模块,能够独立进行AD转换。每个硬件转换单元可服务多个通道,这些通道由 多路连接器 连接到转换单元上,用户可灵活配置每个转换单元的转换通道。

每个硬件转换单元都是独立工作的,它所包含的通道可灵活进行组合,也就是我们常说的Adc Group。

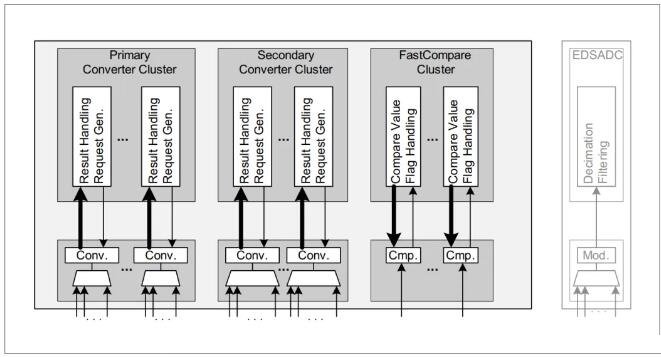

EVADC模块包含三个簇,每个簇有多个硬件转换单元,也就是按特性分为三组:

- Primary converter cluster:主转换簇,配备8:1多路选择器,8阶段转换序列,最低0.5μs转换时长;

- Secondary converter cluster:次转换簇,配备16:1多路选择器,16阶段转换序列,最低1μs转换时长;

- Fast compare cluster:快速比较簇,单通道,更新速率最快0.2μs。

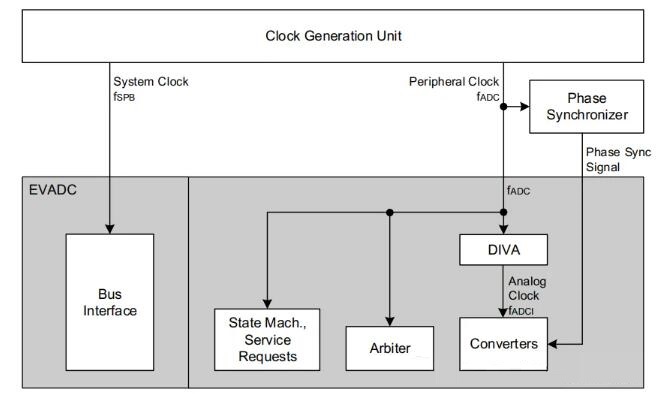

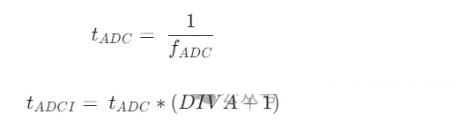

ADC模块的总时钟来源于 fADC ,除了用于ADC模块的转换时钟源以外,还可以用于仲裁、不同单元的同步等功能。 每个硬件转换单元 有独立的时钟分频器 DIVA(GxANCFG.DIVA) ,用于分出转换模块使用的时钟频率 fADCI 。计算公式为fADCI=fADC/(DIVA+1)。fADCI时钟频率一般为20MHz~40MHz,不宜太高,否则噪声过大。

fSPB时钟 用于CPU对ADC模块的寄存器访问时钟。

硬件转换单元可以设置4种转换模式,通过单元内部的 GxARBCFG.ANONS寄存器 决定:

- ANONS = 11b : Normal Operation,普通模式 ,硬件转换单元持续处于工作状态,出现转换请求就能够立刻执行;

- ANONS = 10b: Fast Standby mode,待机快速模式 ,当没有转换请求时,硬件单元会进入休眠模式,当出现转换请求时会被自动唤醒,唤醒的延时大约为 1µs ;但能够降低功耗;

- ANONS = 01b: SlowStandby mode,待机慢速模式 ,当没有转换请求时,硬件单元会进入休眠模式,当出现转换请求时会被自动唤醒,唤醒的延时大约为 5µs ;但最大程度降低功耗;

- ANONS = 00b: Converter switched Off,关机模式 ,复位或启动之后默认模式,转换请求之前需要先设置ANONS以离开关机模式。

以上四种模式中有三种工作模式, 普通模式 是我们最常用也是最简单的模式。如果系统对 功耗 有较为严格的要求,可以考虑后续两种模式,但要充分衡量系统对 转换实时性 的要求。如果要求采样频率仅为毫秒级,则结合GTM等定时器进行 持续定时触发 即可。

2.2 ADC kernel 硬件转换单元结构

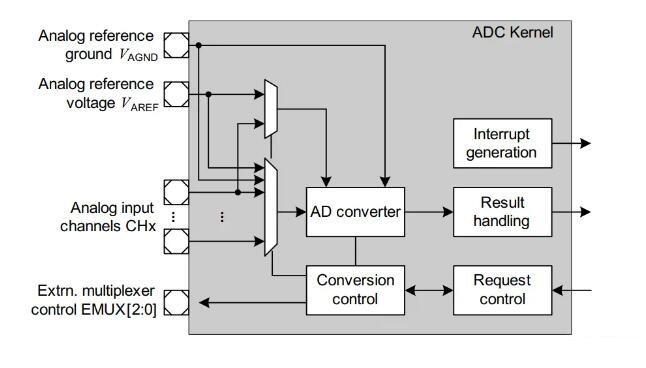

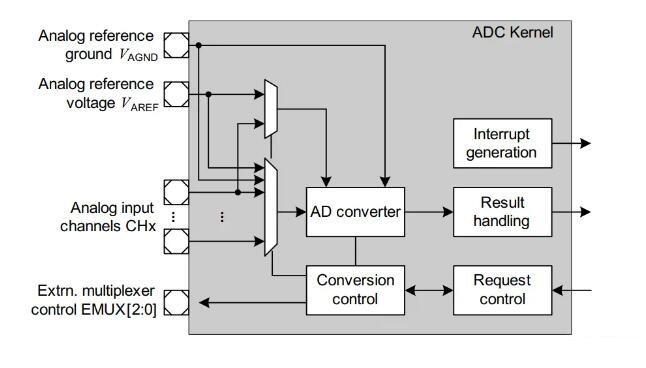

我们来看单个硬件转换单元,它的功能框图如下图所示。

它的外部连接主要有以下部分:

- Analog reference ground VAGND:ADC 参考GND ;

- Analog reference voltage VAREF:ADC 参考电压 ,也是ADC采样的量程;

- Analog input channels CHx:ADC 输入通道 ,也就是被测源;

- Extrn.multiplexer control EMUX: 多路复用控制器 ,配合 外部复用开关 使用,一般很少使用;

它的内部主要有以下几个模块:

- Request Control:请求控制器,主要负责处理转换请求,仲裁等;

- AD Converter:AD转换器,主要负责逐次逼近转换的实现;

- Input Channel Selection:输入选择器(途中的通道输入连接处),用于实现通道组合,也就是我们说的Adc Group;

- Conversion Control:转换控制器,主要负责转换模式的设置,如滤波、预充等;

- Result Handling:结果处理器;

- Interrupt Generation:中断发生单元,主要用于向IR模块产生中断信号;

当软件或者硬件向一个EVADC模块发送请求,由 请求控制器 进行仲裁和处理,然后由 转换控制器 根据配置来控制对应的通道转换,然后由 AD转换器 进行AD转换,最终结果输入到 结果处理器 中,并通过 中断发生单元 根据对应的事件触发中断。

2.2.1 Request Control

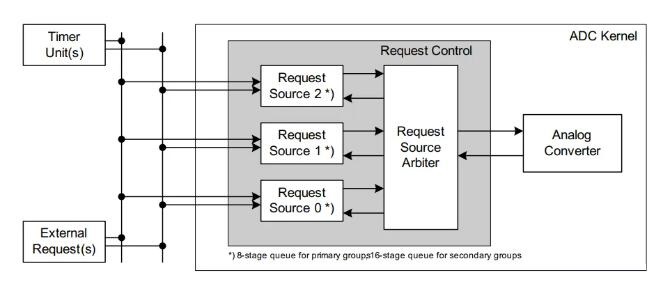

下面我们依次介绍ADC硬件转换单元中的模块,首先是请求控制器Request Control。

每个硬件转换单元内部有三个可配置的转换请求源,可以配置为多种来源,有 硬件触发 如GTM定时采样、 软件触发 、 ADC内部定时器触发 。由于每个ADC硬件可能存在多个Adc Group,多个Group同时进行请求的时候则需要仲裁(使能了优先级的情况),请求控制器中存在仲裁处理单元,能够对多个同时到达的转换请求进行仲裁,当一个高优先级请求到达,而当前低优先级请求正在执行时,根据配置有三种处理方式:

在我们平常使用ADC时,一般一个ADC转换单元里只配置一个Group,该Group包含了这个转换单元里的所有通道,ADC请求一次则会执行所有通道,因此很少会用到优先级。

2.2.2 Input Channel Selection

我们看到转换控制器中有三个转换源(Request Source),这里对应我们的Group,当我们在一个Group里配置包含哪些通道,最终硬件设置的是这三个转换源。也就是说,每个转换源转换哪些通道,在Group中设定好了,我们只需要请求该转换源,就可以执行对应Group中所有通道的转换。

2.2.3 Conversion Control

转换控制这里包含了通道转换的相关参数,包括 充能时间 、 降噪模式 等,全部包含在InputClass中,这个概念我们后续在配置中会介绍。

2.2.4 Analog/Digital Converter

Converter是实现逐次逼近转换的物理单元,执行通道的采样转换。当选定通道之后,AD转换器中有一个采样-保持单元,连接到SAR上,将逐次逼近的采样结果输送到结果处理单元中。

2.2.5 Result Handling

每个ADC通道有16个结果寄存器,转换通道与结果寄存器的连接关系是可以灵活连接的。比如我只选了通道1、4、7,我可以选择把他们的结果依次存放到结果寄存器1、2、3中。如果使用了 wait-for-read 模式,每次结果产生后如果没有被读取(软件或DMA读取),则下一次转换请求会被拒绝。另外结果寄存器还能构成FIFO队列,而不是直接覆盖。

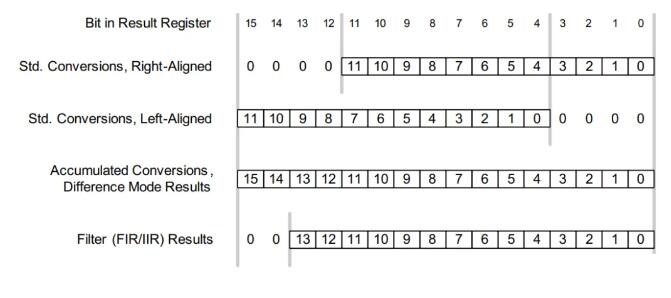

值得一提的是,EVADC的转换精度是12bit,但是结果寄存器是16位宽,,默认模式下可以选择使用前12位或者后12位,如果使用了累积模式,也就是多次采样取均值,则能够启用全部16位。

2.2.6 Service Request Generation

TriCore架构中中断称为服务请求(Service Request)。ADC模块能够产生三个类型的中断:

- Source Event :转换请求完成中断,这个是我们主要使用的中断类型,当一个源请求完成后,向IR模块发送中断信号;每个硬件转换单元有4个中断输出信号,一般将前三个配置为三个Source对应的中断信号;

- Channel Event :通道转换完成事件,这个中断事件可以和 结果限制检查 配合使用,当某个通道的结果位于我们指定的范围时(一般是过高或过低),可以产生中断信号;

- Result events :结果可用事件,这个中断是配合累积转换序列使用的,累积转换的结果是多次的,因此如果使用该模式,以结果可用事件的中断信号为准。

这里需要注意的是,EVADC的中断信号并不是固定连接的,而是可以灵活配置的。

对于硬件单元内部来说,因为一个硬件单元有三个内部的请求源,所以可以产生三个Source Event中断信号;有8/16个通道,可以产生对应数量的Channel Event中断信号。

每个硬件单元有4个中断输出引脚(Service Request Output Line),这些引脚向外连接到中断路由器中。用户可以通过配置,选择如何使用这4个中断引脚。

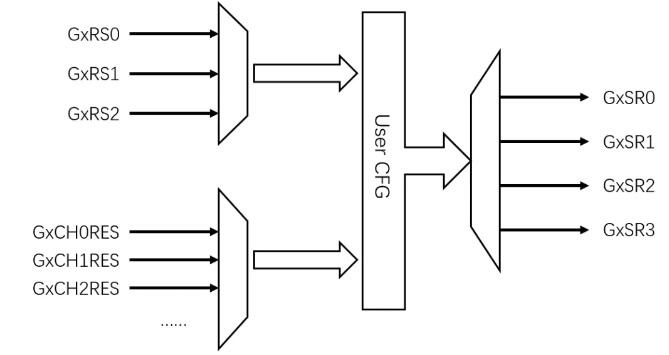

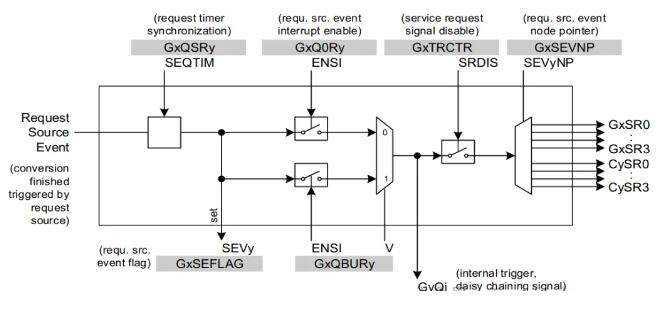

下图描述了中断输出信号的配置关系,Result Event中断使用场景较少,图中未画出。

2.3 转换请求与仲裁

接下来我们将描述从一个转换请求到最终采样到ADC值的过程,本节将着重描述转换的请求与仲裁。

2.3.1 转换请求的产生

转换队列

在AD转换的使用中,最常用的是一个转换请求执行一组通道转换,而这组通道需要一个载体,告诉硬件哪些通道是需要执行的,其顺序如何,这个载体就是 转换队列(Request Queue) 。主转换簇中的硬件单元支持8级队列(通道数也为8),次转换簇最多支持16级队列(通道数为16),因此一个队列能够完成所有通道转换的配置。

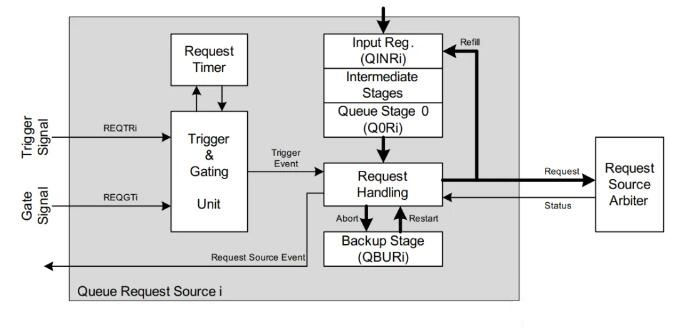

前面我们提到,一个硬件转换单元内部有3个转换源控制单元,每个转换源控制单元内部结构如下:

在框图的右上角,我们可以看到一个队列,在请求转换之前,需要先配置队列。向 GxQINRi (x为硬件单元,i为请求源)寄存器写入通道的相关配置,就会将通道请求压入队列中。QINR的具体位域内容根据通道配置设置即可。

在MCAL驱动代码中,队列的最后一条通道请求的中断服务请求 GxQINRi.ENSI 需打开,以发送队列转换完成信号。如果是硬件触发,则队列第一条的 GxQINRi.EXTR 需置位,以等待硬件触发。

另外如果是硬件触发或者软件触发连续转换,则需要将 GxQINRi.RF 置位,这样每个完成的转换会自动回到队列末尾,以实现自动填充,无需软件重复操作。

如果是需要硬件触发,则需要在 GxQCTRLi (x为硬件单元,i为请求源)寄存器配置相应的触发设置。

触发方式

完成了转换队列的配置之后,下一步就是进行触发了,EVADC转换请求的触发方式一共有三种:

- 软件触发 :顾名思义,由软件通过写寄存器执行一次转换请求,GxQMRi.TREV=1;

- 内部定时器触发 :EVADC硬件转换单元提供了内部定时器,用于定时触发,但是位宽仅10位,而ADC的频率一般为MHz级别,所以能够实现的延时仅微秒级别,所以一般不使用该方式;

- 外部触发 :这种触发的可配置性非常强,能够通过多种方式触发,包括但不限于外部引脚、GTM定时器触发;

另外转换的请求可选择是 单次 还是 连续 (Single Mode or Continuous Mode),单次的每次转换都需要一次触发;连续模式下一旦触发就会连续进行转换。

这里值得一提的是,外部触发支持门控触发,我们就能够通过外部引脚控制AD转换的开闭。

2.3.2 转换请求仲裁

通常情况下我们一个硬件单元只设置一个Group,对应到请求源0。但是在某些场景下,受限于硬件电路设计,功能需求等因素,我们会应对同一硬件单元中存在不同请求源,且需要按照优先级来进行处理的情况。这个时候我们就会用到EVADC的请求仲裁功能。

我们可以通过寄存器 GxARBPR 来配置不同请求源的优先级,这样在多个请求同时出现的时候,仲裁单元就会选取优先级最高的先进行处理。

另外值得一提的是,如果使用了跨硬件单元 同步处理功能 ,则该同步触发源的优先级是最高的。

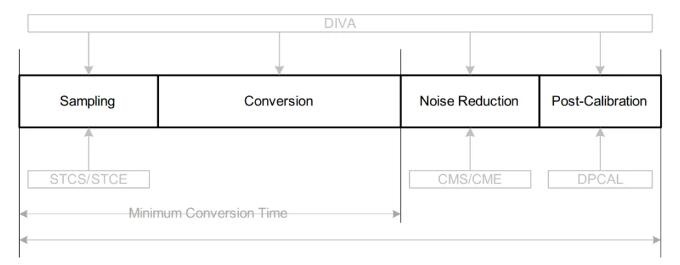

2.4 硬件转换流程

本节我们介绍下转换的流程,这些流程是转换请求被接收后,由硬件执行的,无需软件操作。但是熟悉了这些流程后,读者能够更好地理解ADC模块的功能和相关配置。

系统启动后,硬件会进行AD转换器的标定,以对转换进行校准,该流程 仅在初始化阶段执行 。

在运行阶段,当接收到转换请求,并完成仲裁之后,硬件即开始进行AD转换。AD转换包括4个步骤:充能、转换、降噪和后标定。其中 采样和转换 是必须的, 降噪和后标定 是可选的。

2.4.1 初始化标定流程

在硬件转换单元启动之后,会按照用户设定的时间 (GxANCFG.CALSTC) 进行标定,该操作只在启动阶段执行一次,后续转换不再执行。转换时间计算公式如下:

其中:

向 GLOBCFG.SUCAL 写1执行标定流程。

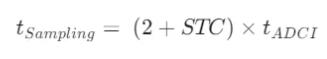

2.4.2 Sampling充能流程

硬件开始转换的第一个流程是 充能 ,充能是将输入电压或参考电压充入转换电容中。具体的硬件逻辑此处不作详细解释,感兴趣的读者可以自行查阅资料。

充能的时间是可配置的,颗粒度是 ADCI时钟周期(GxIClass.STCS) ,最低时间是 两个 ADCI时钟周期(STCS=0)。充能时间配置越长,采样越稳定,但采样耗时越长。一般使用默认的最低充能时间就够了。但是如果该硬件单元的时钟频率配置过高,则建议增加充能时间,否则充能不充分会导致采样结果出现较大偏差。

另外Aurxi芯片的EVADC模块还有 输入缓冲功能(Input Buffer) ,即在充能阶段之前先进入预充能,该功能能够增强信号输入能力,防止抖动。输入缓冲的颗粒度也是ADCI时钟周期,可配置为0、8、16、32。值得注意的是,如果配置了输入缓冲功能,配置的充能时长需要至少覆盖 预充和充能 两个阶段。

充能阶段的耗时为:

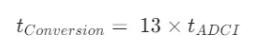

2.4.3 Conversion转换流程

充能完毕之后转换单元就需要对充能的电压进行结果转换,我们采用的是逐次逼近原理,所以转换的时间和采样精度,也就是结果位宽是成正比的。我们的精度是12bit,因此采样阶段的耗时为:

2.4.4 Noise Reduction降噪流程

熟悉信号处理的读者都知道,信号的传递难免是有噪声的。噪声可能是由传感器本身产生的,也可能是在传递过程中产生的,另外AD转换作为一个数字模块嵌入在MCU中,也可能存在一些噪声。因此在进行AD采样时,如果对信号的要求比较高,则需要进行降噪。Aurix的EVADC提供了降噪功能,作为硬件转换流程的可选步骤存在,包括如下几种方式。

Noise-Reduction Conversions 降噪转换

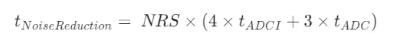

该功能是在转换阶段增加额外的流程,对转换进行优化,可选1、3、7降噪强度。降噪时间为:

Spread Early Sample Point 扩展早期采样点

除了静态噪声外,同步噪声不能通过采样消除。扩展早期采样点特性通过以伪随机数步长,来移动采样相位的末端,来衰减同步噪声。通过配置GxICLASSi.CMS/CME来设置。如果使用了该特性,充能阶段会被随机缩减最多100ns,这个需要计算到采样时长中。

Accumulated Conversions 累积转换

除了对信号进行降噪以外,还能通过累积转换求平均值的方法来获取可靠的数据。用户可设定2~16个转换结果,最后硬件会自动进行累加。

2.4.5 Post-Calibration 后标定流程

后标定流程可以被添加到转换的末尾,用于矫正初始化中标定效果的老化。据手册描述,老化其实是非常慢的,而且后标定流程使得转换电容放电,因此推荐不使用该功能。如果使用了,后标定时间为:

2.4.6 转换总时间

介绍完了硬件转换的流程之后,我们来归纳转换总时间的计算方法。除了充能、转换这两个必要流程,以及降噪、后标定这两个可选流程,每次转换还有一个固定的硬件状态机切换流程,占3个tADC。所以一次转换的总时间为:

代入上面的详细值得到转换总时间:

假设我们ADC时钟频率为160MHz,取DIVA=7,所以fADCI=20MHz,tADC=6.25ns,tADCI=50ns。我们取STC=0,NRS=1,CALSTC=1,则转换总时间为T=1.31µs。如果我们不进行降噪和后标定,转换总时间为T=0.768µs。

2.5 转换结果与中断

在硬件完成了通道转换之后,就要处理转换结果,将值送到指定的寄存器;而且在一个转换队列全部完成之后,要产生对应的中断,将信号送到中断路由器,以供CPU或DMA进行处理。

2.5.1 转换结果处理

结果寄存器

EVADC每个硬件单元有自己的与通道数对应的结果寄存器 GxRESy ,在我们设置结果关联时,我们可以选择通道与结果号一一对应,即通道X的结果保存到结果寄存器X中。事实证明,这种配置方式使得软件容易维护。

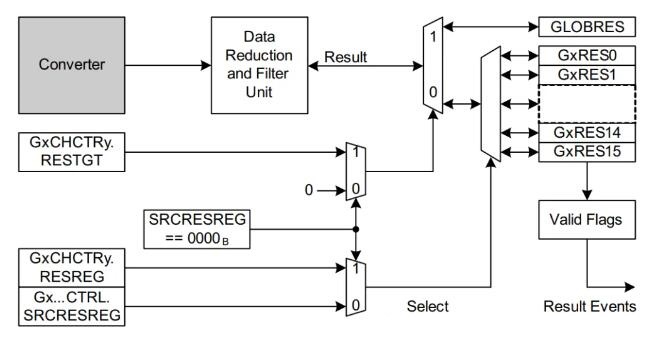

除了单元内部的结果寄存器外,EVADC还有一个全局结果寄存器GLOB.RES,以方便进行跨通道的关联数据处理,一般情况下是每个硬件单元配置使用各自的单元内部结果寄存器。其结果输出设定参考下面这张寄存器逻辑图。

数据对齐

前面提到,EVADC的精度是12位,但是其结果寄存器中对应的结果位域是16位,以供其他功能使用。一般情况下我们是使用右对齐12位。

Wait-for-read模式

EVADC模块还提供了一个等待读取模式,在该模式下,如果新的结果没有被CPU或DMA读取过,则该通道的转换请求无法执行(Debug读取不算)。

FIFO Buffer

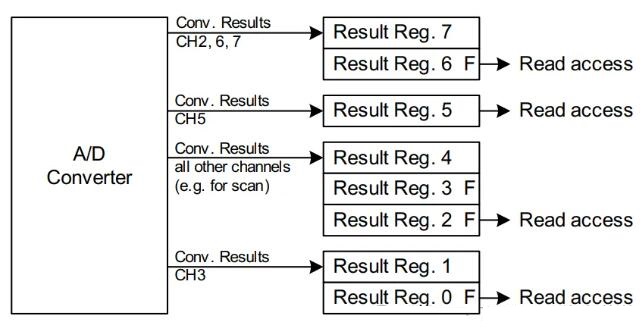

EVADC提供了FIFO功能,即两个或两个以上相邻的结果寄存器,组成一个先进先出的队列,硬件会将用户指定的转换通道的结果保存到队列中,用户读取其中序号最小的结果寄存器即可取出队列中数据。

下图中结果寄存器0、1组成队列供通道3使用,2、3、4组成队列供其他通道使用,6、7组成队列供通道2、6、7使用。这种配置一般是应对需要多次采样结果结合使用的场景。

2.5.2 转换结果中断

前面我们提到,EVADC模块的中断信号类型有三种,转换请求完成中断、通道完成中断和结果可用中断,他们与4个中断输出引脚的连接是可配置的。

通常情况下,对于一个硬件单元,我们一般将三个请求源的中断信号分别配置给前三个中断输出引脚,用于AD转换结果的处理;将所有的通道结果中断信号,配置给第4个中断输出引脚,用于结果异常处理。

对于请求源中断信号,其连接配置参考下图对应的寄存器:

当请求源完成中断信号产生,则对应的 GxSEFLAG 中的对应位域会置位,可使用 GxSEFCLR 寄存器取清除。

当通道中断信号产生,则对应的 GxCEFLAG 中的对应位域会置位,可使用 GxCEFCLR 寄存器取清除。

当结果可用中断信号产生,则对应的 GxREFLAG 中的对应位域会置位,可使用 GxREFCLR 寄存器取清除。

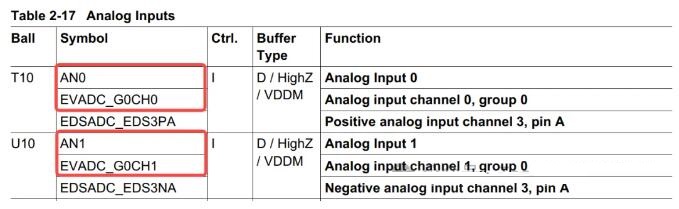

2.6 引脚连接

ADC的硬件引脚连接不像Port模块,能够灵活配置,它的连接还是比较固定的,比如硬件引脚的AN0对应的就是EVADC模块的G0CH0,AN8对应的就是G1CH0(G0通道数为8,AN号依次排开)。具体的连接直接查阅芯片DataSheet中的 Analog Inputs 表格。

3 MCAL配置示例

介绍完了ADC的硬件原理和整体流程,下面我们结合示例来对EVADC模块在EB工具中的MCAL配置进行说明。这里我们使用Demo工程中自带的软件触发示例,读者也可以结合之前GTM介绍文章中描述的GTM->ADC硬件触发,实现ADC自动定时采样。

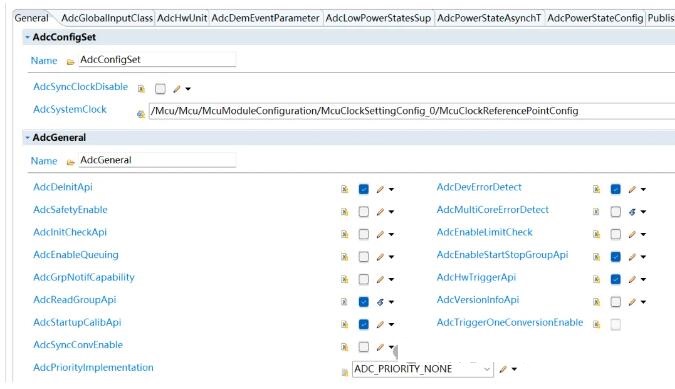

3.1 AdcGeneral

首先我们来到General界面,这里按照实际使用需要配置即可,一般都是软件使能的配置;

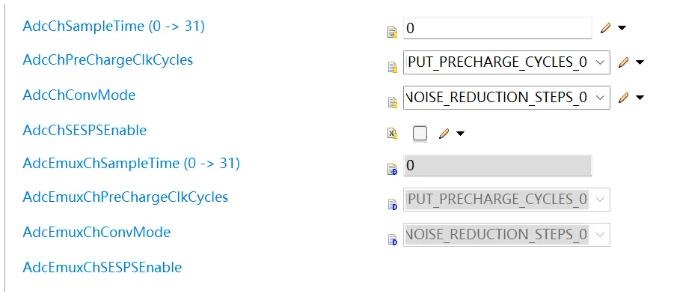

3.2 AdcGlobalInputClass

然后我们来到AdcGlobalInputClass,这里解释一下,EVADC模块的通道配置有一个 InputClass 的概念,即输入 配置类 ,该配置类包含了一些通道配置。预设了配置类之后,每个通道可独立选择使用指定的配置类。对于整个EVADC模块,存在两组Global Input Class,即 全局配置类 。然后每个硬件转换单元有自己私有的两个Input Class,即 Group配置类 。每个ADC通道可以在全局配置类和所在硬件单元的Group配置类中进行选择。下面那我们介绍配置类的配置内容。

AdcChSampleTime充能时间

前面我们提到了充能阶段的充能时间是可配置的(最小为2*tADCI),通过GxIClass.STCS进行设置,总充能时间为(2+STCS)*tADCI。充能时间越长,采样越充分,一般取STCS=0即可,如果fADCI的频率较高,考虑增大充能时间参数。

AdcChPreCharge ClkCycles 输入缓冲时间

如果在充能阶段使用了Input Buffer,则可配置其缓冲时间,它的配置档位是0、8、16、32个fADCI。通过 GxIClass.AIPS 控制。这里我们不使用输入缓冲。

AdcChConvMode降噪模式

降噪流程是可选的,配置档位NRS是0、1、3、7,具体时间参考前文降噪流程计算公式。通过GxIClass.CMS控制。这里我们不使用降噪。

Spread Early Sample Point 扩展早期采样点(AdcChSESPSEnable)

扩展早期采样点可在Input Class配置中使能,通过 GxIClass.SESPS 控制。

External Multiplexer配置

EVADC支持对外置的多路选择控制进行配置,因此在Input Class中支持对应的配置参数,这里不作详细描述。

3.3 AdcHwUnit

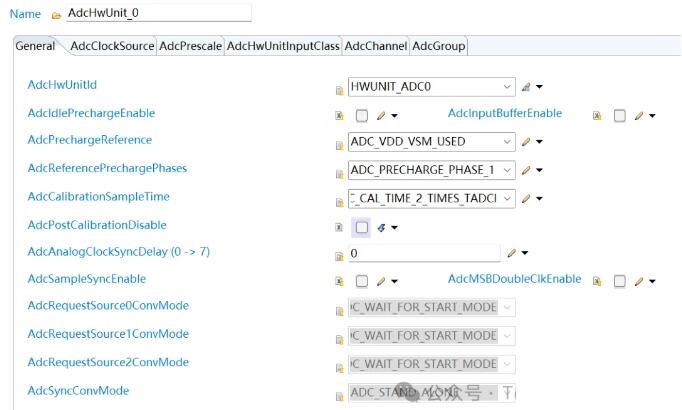

然后我们来到AdcHwUnit_0,进行硬件转换单元相关配置。

AdcIdlePrechargeEnable & AdcInputBufferEnable & AdcPrechargeReference预充控制

Aurix的EVADC模块有三种预充,第一种是通道空闲预充,是在通道空闲的时候将其预充到参考电压的一半,通过 GxANCFG.IPE 控制;第二种是前文提到的Input Buffer预充,通过 GxANCFG.BE 控制使能,并通过通道配置控制预充时间;第三种是转换的时候通过参考电压对电容进行预充,能够实现最大精度,通过 GxANCFG.RPE 控制,该功能默认是使能的。这里我们只使用参考电压的预充。

AdcCalibrationSampleTime标定时长 & AdcPostCalibrationDisable后标定关闭

如前所述,标定作为可选功能,通过 GxANCFG.DPCAL (置1关闭)控制使能,通过 GxANCFG.CALSTC 控制时间参数CALSTC。后标定使能默认是打开的(勾选为关闭),这里我们使用后标定功能,默认标定时间参数选择2。

AdcAnalogClockSyncDelay & AdcSampleSyncEnable 同步转换

不同的硬件转换单元之间能够进行同步AD转换,通过配置可以实现。通过GxANCFG.SSE控制使能。这里我们不使用。

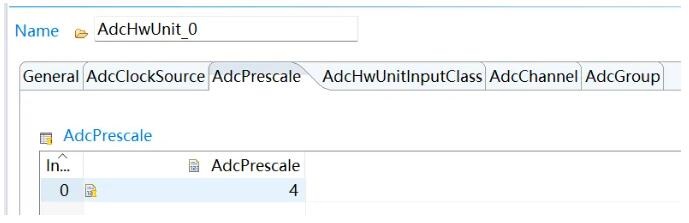

AdcPrescale硬件单元分频

然后我们来到AdcPrescale选项卡配置时钟分频,注意这里配置的值实际是DIVA+1,如果你想配置4倍分频,这里直接配4,工具会将DIVA写成3。

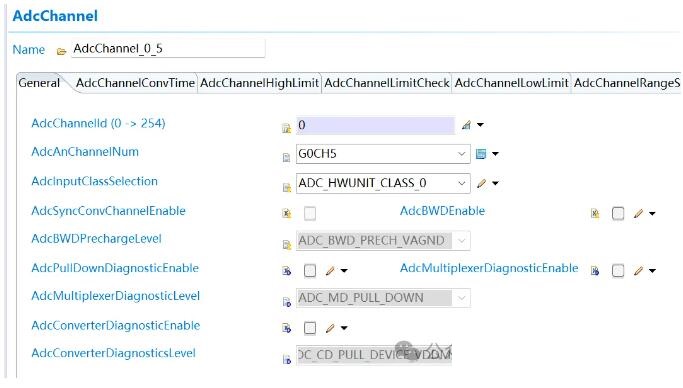

3.4 AdcChannel

通道配置这里没有什么特别的,就是选定你目标通道所连接的硬件引脚,选择一下InputClass。

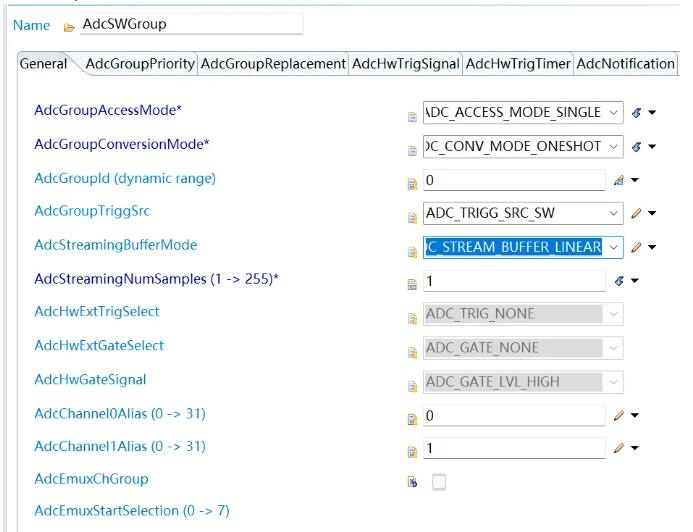

3.5 AdcGroup

AdcGroup中配置的就是我们的转换请求源的选项,首先我们来到General中。

AdcGroupAccessMode Adc组访问模式

这个配置可选择是单次还是Stream模式,单次很好理解,一次一停,一组Buffer;Streaming就是能够进行多次转换,比如启动一次,转换5次,将5次的值存放到用户指定的Buffer中。

AdcGroupConversionMode Adc组转换模式

这里我们是单次转换,选择oneshot,如果有Streaming需求的需要配置为Continuous。

AdcGroupId

软件GroupID识别号。

AdcGroupTriggSrc触发源

这里可以选择是硬件触发还是软件触发,根据实际需求配置。

AdcStreamingBufferMode缓存区模式

这里如果是单次或Streaming模式的话,需要配置成Linear。如果是连续,且不使用Streaming模式,也就是一次触发就永远持续转换,则需要使用Circular。

AdcStreamingNumSamples Streaming采样次数

这里定义了Streaming模式下单次触发的采样次数,比如定义了5,则一次触发会进行5次转换,每次转换后也都会进一次ADC中断。这里需要注意的是,软件初始给的Buffer一定要够用,一个结果占据uint16,如果该参数为5,Group中配置通道数为8,则Buffer尺寸需要为5*8*uint16,下一次再触发则会从头覆盖该buffer。这里我们是单次转换,所以配置为1。

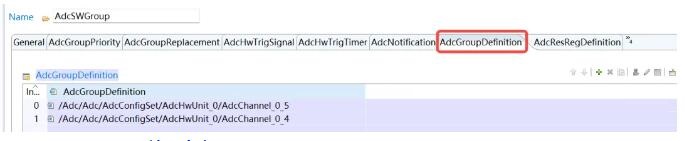

AdcGroupDefinition组定义

然后我们来到下一个选项卡AdcGroupDefinition,这个选项卡中定义了Group中所包含的通道,也就是我们前面说的压入转换队列中的内容。一次转换请求就是将这些通道依次进行转换,全部转换完成触发一个中断。

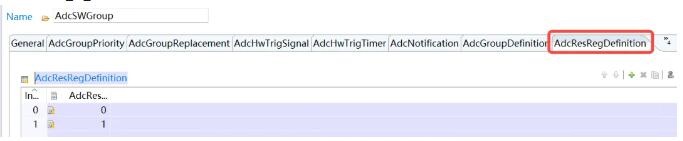

AdcResDefinition结果定义

这个选项卡中定义了结果寄存器的选择,这里和组定义是一一对应的,比如我这里Channel_0_5结果存放到Res0中。

中断相关的配置这里不做描述了,读者可以参考之前中断模块的文章,在Irq模块中给G0S0进行配置即可,MCAL代码对于非同时拥有软、硬触发源的单元默认使用G0S0。

AdcNotification

这个选项卡中可以配置一个Notification函数,完成后ADC中断内会调用该函数通知用户,形式为void FuncXXXX(void)。

3.6 示例代码

完成了配置我们就可以编写相应的代码了,首先我们进行相关初始化,需要进行Adc模块初始化,中断寄存器初始化,并打开中断。然后设置GroupBuffer,这里我使用单次转换,因此Buffer数量等于Group通道数。

这里非常值得注意的是, Buffer一定不能给小了 ,因为这里给的是数组起始地址,底层驱动是不知道Buffer尺寸的,如果给小了,则其后续的其他数据就会被 覆盖 。

Adc_Init(&Adc_Config); /* Adc Init */

IrqAdc_Init(); /* Irq Init */

SRC_VADCG0SR0.B.SRE = 1; /* Enable EVADC Group0 Source0 INT */

Adc_ValueGroupType Adc0GroupSWResult[2];; /* 注意:该变量为全局变量 */

Adc_SetupResultBuffer(AdcConf_AdcGroup_AdcSWGroup, Adc0GroupSWResult); /* Setup Buffer */

|

然后我们在软件中周期进行转换的软触发:

Adc_StartGroupConversion(AdcConf_AdcGroup_AdcSWGroup); /* Start Group Conversion */ |

这样就完成了简单的代码,结果Buffer会在中断函数中更新,如果你没有使用中断函数,也可以使用中断信号连接DMA,直接从结果寄存器中搬运转换结果。

4 小结

本文介绍了Infineon Aurix 2G TC3XX系列EVADC模块的原理及功能,内部结构,并描述了其内部转换请求的处理逻辑,以及硬件转换的详细流程,最后通过使用示例详细介绍了MCAL的配置参数及使用方法,通过理论和实践结合,帮助读者掌握该模块。

|