һ���γ���Ƶ���Ŀ

����Ƕ��ʽCISCģ�ͻ�����ͨ·��ͼ

�������������(CISCģ�ͻ�)�����ṹ��ͼ

�ġ�ģ�ͻ���ָ��ϵͳ��ָ���ʽ

�塢����ָ�����������ͼ

����Ƕ��ʽCISCģ�ͻ��Ķ����·ͼ

�ߡ��������Դ����

�ˡ���������Դ����

�š������ʽ��ָ������

ʮ�����沨��ͼ�������

ʮһ����������ͷ����Լ��ĵ����

ʮ���������嵥

1.��������״̬�����Ĵ�����Ԫ

2.ͨ�üĴ�����ԪLS273

3.��ַ�Ĵ�����ԪLS273

4.ָ��Ĵ�����ԪLS273

5.1:2������FEN2

6.4ѡ1����ѡ������ԪMUX4

7.5ѡ1����ѡ������ԪMUX5

8.�����������ԪPC

9.���洢����ԪROM

10.ʱ���������ԪCOUNTER

11.�������Ƶ�ԪCROM

һ���γ���Ƶ���Ŀ

A�ࣺ�������10��������8λ�����Ʋ����ʾ��������M������RAM���������С�ĸ�����

����Ƕ��ʽCISCģ�ͻ�����ͨ·��ͼ

�������������(CISCģ�ͻ�)�����ṹ��ͼ

˵����

��T4���γ�ָ�����ַ�������ʿ��ƴ洢������T2���ϱ��ص���ʱ����������ָ�����ָ��Ĵ�������ͼ�е�����Ĵ�������ַ�Ĵ�����

�ġ�ģ�ͻ���ָ��ϵͳ��ָ���ʽ

(1)I/Oָ��

���루IN1��ָ����õ��ֽ�ָ����ʽ���£�

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

�� �� |

Rd |

�����OUT1��

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

Rs |

�� �� |

RsָԴ�Ĵ�����RdָĿ�ļĴ�����

(2)����ָ��

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

�� �� |

Rd |

(3)ת��ָ��

����ת��ָ�JB��JN����������ת��ָ�JMP�����õ��ֽ�ָ��

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

�� ��

�� �� |

| �� ַ |

˵��������ַ���е�ֵ����Ҫת�Ƶĵ�ֵַ

(4)�Ƚ�ָ�CMP����MOVָ��

�Ƚ�ָ�CMP����MOV1���õ��ֽ�ָ���ʽ���£�

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

Rs |

Rd |

MOV����˫�ֽ�ָ���ʽ���£�

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

�� �� |

Rd |

| �� ַ |

(5)�Ĵ����䴫��ָ��

MOV3���õ��ֽ�ָ���ʽ���£�

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

Rs |

Rd |

MOV����˫�ֽ�ָ���ʽ���£�

(6)�Ĵ�����ַѰַ��ָ��

MOV1���õ��ֽ�ָ���ʽ���£�

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

[Rs] |

Rd |

MOV2���õ��ֽ�ָ���ʽ���£�

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

Rs |

[Rd] |

(7)��������ָ��

TEST���õ��ֽ�ָ���ʽ���£�

| 7 6 5 4 |

3 2 |

1 0 |

| ������ |

�� �� |

Rd |

�ɴ˿ɼ�������12������ָ��±��г���ÿ��ָ��ĸ�ʽ�������ź�ָ��ܡ�

| ���Ƿ��� |

ָ���ʽ |

���� |

| TEST Rd |

|

����

Rd

�Ĵ����е�ֵ�Ƿ�Ϊ���� |

| MOV3 Rs ,Rd |

|

(Rs)��(Rd) |

| IN1 Rd |

|

�����ݴ浽

Rd

�Ĵ��� |

| MOV Rd, data |

|

data��Rd |

| MOV1 [Rs], Rd |

|

[Rs]��(Rd) |

| MOV2 Rs, [Rd] |

|

(Rs)��[Rd] |

| CMP Rs, Rd |

|

(Rs) �C (Rd)������

CY

��

ZI |

| JB addr |

|

��С�ڣ���

addr��PC |

| JN addr |

|

��������

addr��PC |

| INC Rd |

|

(Rd) + 1��Rd |

| JMP addr |

|

addr��PC |

| OUT Rs |

|

(Rs)��LED |

˵����

�ٶ�Rs��Rd�Ĺ涨��

| Rs��Rd |

ѡ���ļĴ��� |

| 0 0 |

R0 |

| 0 1 |

R1 |

| 1 0 |

R2 |

| 1 1 |

R3 |

��ģ�ͻ��涨���ݵı�ʾ���ö������������ʾ�����ֳ�Ϊ8λ�����ʽ���£�

| 7 |

6 5 4 3 2 1 0 |

| ����λ |

� |

�塢����ָ�����������ͼ

����Ƕ��ʽCISCģ�ͻ��Ķ����·ͼ

�ߡ��������Դ����

ͬ��������Ŀ��д�������Դ�����㷨˼��Ϊ��R0�Ĵ�����ʼ��Ϊ1��R1�Ĵ�����ʼ��Ϊ11��R3�Ĵ���������������ݣ�Ȼ��R3�е���������R0�Ĵ����е���Ϊ��ַ��RAM�У�R0�Ĵ�������һ���ٺ�R1�Ĵ����е������бȽϣ����С������������һ���������ѭ��ʮ�Σ��������ʮ��������RAM�С���R0�Ĵ���������R1�����ʱ������븺���ж�������ıȽϡ�

R0�Ĵ�����ʼ��Ϊ1��R1�Ĵ�����ʼ��Ϊ11��R2�Ĵ�����ʼ��ΪFF����-1������RAM����R0�е���Ϊ��ַ�ĵ���ȡ��������R3�У�Ȼ��R0����һ��Ϊȡ��һ����������ͬʱ�ж��Ƿ��Ѿ�ȡ����ʮ����������������R3�е���ʱ��Ϊ�������������������L1����RAM��ȡ��һ����������Ǹ��������R2�е������бȽϡ����R3�е�����R2�е�����������L1����RAM��ȡ��һ����������R2�е����滻ΪR3�е���������ÿ�αȽ����R2�ж����������С�ĸ��������ѭ��ʮ�Σ�������R2�е���������С�ĸ�����

MOV R0,1 /��������1��R0

MOV R1,11 /��������11��R1��R2���ڼ�����

L1: IN1 R3 /R3�������������

MOV2 R3,[R0] /дRAM����ַ������R0��

INC R0 /R0�Լ�һ

CMP R0,R1 /��R1�е�����R0�е������бȽϣ�����CY/FC��ZI/FZ

JB L1 /С��,��ת��L1��ִ��

MOV R0,1 /��������1��R0

MOV R1,11 /��������11��R0

MOV R2,FFH /��������FFH��R0

L2: MOV1 [R0],R3 /��RAM����ַ������R0��

INC R0 /R0�е����Լ�һ

CMP R1,R0 /��R1�е�����R0�е������бȽϣ�����CY/FC��ZI/FZ

JB L5 /С��,��ת��L5��ִ��

TEST R3 /����R3�е����Ƿ�Ϊ����

JN L3 /R3�е����Ǹ���ʱ��������L3ִ��

JMP L2 /������ת��L2��ִ�У�������RAM��ȡ��һ����

L3: CMP R3,R2 /��R3�е�����R1�е������бȽϣ�����CY/FC��ZI/FZ

JB L4 /С��,��ת��L4��ִ��

JMP L2 /������ת��L2��ִ�У�������RAM��ȡ��һ����

L4: MOV3 R3,R2 /��R3�е������浽R2�У�R2һֱ���������С�ĸ���

JMP L2 /������ת��L2��ִ��

L5: OUT1 R2 /���R2�������

JMP L5 /ѭ�����

�ˡ���������Դ����

������Ƶ�ָ���ʽ�����������Դ�����ֹ�ת���ɻ�������Դ����������Ƶ�ģ�ͻ��е�ROM��ȥ���������Դ�����Ӧ�Ļ�������Դ�������£�

//���Ƿ� ��ַ��ʮ�����ƣ� �������� ��������ʮ������ ����

MOV R0,1 00 01110000 70 1��R0

01 00000001 01

MOV R1,11 02 01110001 71 11��R1

03 00001011 0B

L1: IN1 R3 04 01100011 63 (SW)��R3

MOV2 R3,[R0] 05 10011100 9C R3��[R0]

INC R0 06 11010000 D0 (R0)+1��R0

CMP R0,R1 07 10100001 A1 (R0)-(R1)

JB L1 08 10110000 B0 L1��PC

09 00000100 04

MOV R0,1 0A 01110000 70 1��R0

0B 00000001 01

MOV R1,11 0C 01110001 71 11��R1

0D 00001011 0B

MOV R2,FFH 0E 01110010 72 FF��R2

0F 11111111 FF

L2: MOV1 [R0],R3 10 10000011 83 [R0]��R3

INC R0 11 11010000 D0 (R0)+1��R0

CMP R1,R0 12 10100100 A4 (R1)-(R0)

JB L5 13 10110000 B0 L5��PC

14 00100010 22

TEST R3 15 01000011 43 80H<=(R3)

JN L3 16 11000000 C0 L3��PC

17 00011010 1A

JMP L2 18 11100000 E0 L2��PC

19 00010000 10

L3: CMP R3,R2 1A 10101110 AE (R3)-(R2)

JB L4 1B 10110000 B0 L4��PC

1C 00011111 1F

JMP L2 1D 11100000 E0 L2��PC

1E 00010000 10

L4: MOV3 R3,R2 1F 01011110 5E (R3) ��R2

JMP L2 20 11100000 E0 L2��PC

21 00010000 10

L5: OUT1 R2 22 11111000 F8 (R2) ��LED

JMP L5 23 11100000 E0 L5��PC

24 00100010 22

�š������ʽ��ָ������

��1�����ָ���ʽ��ָ������

CISCģ�ͻ�ϵͳʹ�õ�ָ�����ȫˮƽ��ָ��ֳ�Ϊ31λ�����������ֶ�Ϊ25λ��P�ֶ�Ϊ3λ�������ַΪ6λ�����ʽ���£�

��ָ���ʽ����������ͼ��д��ָ������������ʾ����ָ��Ĵ�����������ֶδ���ߵ��Ҵ����������ź�����Ϊ��LOAD��LDPC��LDAR��LDIR��LDRi��RD_B��RS_B��S1��S0��ALU_B��LDAC��LDDR��WR��CS��SW_B��LED_B��LDFR��

| ��ַ |

�����ֶ� |

P1 P2

P3 |

���

��ַ |

| 00 |

000000 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000001 |

| 01 |

000001 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

010000 |

| 02 |

000010 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 03 |

000011 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 04 |

000100 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 05 |

000101 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000110 |

| 06 |

000110 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

000000 |

| 07 |

010111 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 08 |

011000 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 11 |

010001 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 13 |

010011 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

000000 |

| 14 |

010100 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

010011 |

| 15 |

010101 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 16 |

010110 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 17 |

010111 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000010 |

| 18 |

011000 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000011 |

| 19 |

011001 |

1 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000100 |

| 1A |

011010 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000101 |

| 1B |

011011 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

100000 |

| 1C |

011100 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

010001 |

| 1D |

011101 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000111 |

| 1E |

011110 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

001000 |

| 1F |

011111 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

000000 |

| 20 |

100000 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 30 |

110000 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

| 31 |

110001 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

000000 |

��2����Ƶ�ַת������·

��ַת������·�Ǹ�����������ͼ�е����οּ������֧��ַ��������ַ�Ĵ������첽�á�1���ˣ�ʵ����ַ�Ķ�·ת�ơ�

������ַ�Ĵ����еĴ������첽�á�1���˵͵�ƽ��Ч�����A4����A0��Ӧ���첽�á�1�������ź�SE5��SE1��������ʽΪ������A5���첽�á�1����SE6ʵ��δʹ�ã�

SE6<=NOT(NOT FS AND P3 AND T4);

SE5<=NOT((NOT FC OR FZ)AND P2 AND

T4);

SE4<=NOT(I7 AND P1 AND T4);

SE3<=NOT(I6 AND P1 AND T4);

SE2<=NOT(I5 AND P1 AND T4);

SE1<=NOT(I4 AND P1 AND T4);

˵����

������������ʽ�ĺ��壺�ڽ���P��1������ʱ������ָ�������I7��I6��I5��I4����16·��֧���ڽ���P��2������ʱ������״̬��־FC��FZ����2·��֧���ڽ���P��3������ʱ������״̬��־FS����2·��֧��

�ڵ�ַת������·���첽�á�1���ź�SE6��SE1����ʽ��ȷ����P�ֶβ���ʱת����ַ��ȷ��������أ�

ʮ�����沨��ͼ�������

ͼA ��CISCģ�ͻ��ϵķ��沨��ͼ1

ͼB ��CISCģ�ͻ��ϵķ��沨��ͼ2

ͼC ��CISCģ�ͻ��ϵķ��沨��ͼ3

ͼD ��CISCģ�ͻ��ϵķ��沨��ͼ4

ͼE ��CISCģ�ͻ��ϵķ��沨��ͼ5

ͼF ��CISCģ�ͻ��ϵķ��沨��ͼ6

ͼG ��CISCģ�ͻ��ϵķ��沨��ͼ7

ʮһ����������ͷ����Լ��ĵ����

ͨ����ογ���ƣ����ǶԼ�����������һ�����Ե���ʶ��ʹ�ҶԼ�����Ĺ���ԭ�����������˸�����̵���ʶ��ͬʱҲ����������ǰ��ѧ�Ļ�����ԣ��Լ���Ƕ��ʽӲ����ARM����ѧϰ�ṩ�˺ܴ�İ���������������������Ӳ���Ĺ���ԭ��������һ�ֿ�������ĽǶȣ���Ҳ����������ѧ֪ʶ������©������Ҫ���ھ����ѧϰ�в����ֲ���

����ʦ�������ۺ��ҾͿ�ʼѧϰVHDL���ԡ������Ͽ���һЩ���Ž̳̺�Ϳ�ʼ��ʵ��α������Ȱ����ϸ������������Ӷ�ʵ���ˣ��Ը��������Ľṹ��������Ƕ��ʽCISCģ�ͻ��Ľṹ�Լ�MAX+plus

II 10.2 BASELINE���˸���ŵ��˽⡣Ϊʵ�ָ����ӵĹ��ܴ������˻������ڵ������ϵ�����ʱ��Ƕ��ʽCISCģ�ͻ��Ĺ���ԭ�����˽�һ�������⡣��һ�ż��ڼ䣬�Ե�ַת�����������źź�������������˸�������⣬ΪP(3)�������������ۻ�����

�ڽ�������һ��������ڿα��ϵ����ӵĻ����Ͻ��иĶ���������һ��P(3)���ԡ�һ���Ĵ�����RAM�����Ȼ������·ͼ��д�û�����������֪��Ҫ�õ���Щָ�Ȼ�����ָ�����������ͼ��ָ������������ǽ��з���͵��ԡ������������У�����͵��Ի�������ʱ�䡣���ݲ���ͼ���ҳ����ִ���ĵط����������ʱ�����������ѵ������ˣ�����һ��������Ľ���ͻ�������ͬѧ���Գ��������Ļ�����һ���Գ���ķ��������һ��ͼ��������û�����ԣ���������û�д����������Ƿ�д�ԣ�����ָ���Ƿ���ȷ������Բ��ԣ��������˳�������������϶��ܰ���������

��ʵ���룬��Щ����ֶ���һЩ�ܵͼ��Ĵ����罫P(1)��P(2)�������߽ᷴ�ˣ������沨��ͼʱ��ָ������ȫ���ˣ�RAM��д��Ͷ������ݻ��߶��������ݲ���Ԥ�ڵ����ݣ����沨��ͼʱ��RAM����������˺͵�ַ����˵����ݶ�����ȷ�ģ�����Ӧ��д����RAM���ڶ�RAMʱ��RAM�ĵ�ַ����˵�������ȷ��������������ȴ����ȷ������һ������ԭ����RAM�Ķ�дʱ�ԣ�RAM��ʱ�����������沨��ͼ��ʾָ��ִ���ˣ���������Ҫ�Ľ�����������ָ�����д�IJ��Եȡ���Щ������ʵ�����ʱ����һЩ������һ�飬�����Ϳ��Լ��ٴ����õ���ʱ�䡣���ң�����ƺ�ָ��ʱ��һ��Ҫ�Ȳ���һ��ÿһ�����ָ���Ƿ���ȷ�����������ڵ��Ի�����ʱ�Ϳ������ɺܶ࣬������Ľ�����Ե�ԭ����Dz���ָ����ƵIJ��ԣ�������תָ�����ת���ԣ�����һ����ԭ���ǻ�����д�IJ��ԣ�������Դ�Ĵ�����Ŀ�ļĴ����ı���д���ˡ���Ը�����ʱ���Сʱ���������Լ�����Сʱ��������ĵ���ʱ�䡣���Ҫ�����ʦ��ͬѧ������Ҳ�����㽹ͷ�ö�����⣬�ڱ���������ʵ��һ���ܼ��������һ��˼·�ͻ�Ȼ���ʡ�

������һ���µ�Ŭ�������ڽ��˴���Ƴɹ���ɣ�ʵ����A����ĿԤ����Ҫ������й��ܡ�

��ʵ���Ĺ����У��ҶԼ������ϵ�ṹ����һ�������⣬�����Ǽ������ҶԼ����Ӳ�������⣬ΪǶ��ʽ��ѧϰ�ṩ�˺ܴ�İ���������Ҳʹ���Ҹ�����̵ķ������Լ��IJ��㣬��Ҫ����Ŭ����ѧϰ�����磺�Գ��������PC�Ĺ������ⲻ��ȣ�PC��ֵ�͵�AR��PC���1ָ����һ��ָ���

��������Ȼ�����Ԥ����Ҫ��Ļ������ܣ������кܶ���Ҫ���Ƶĵط�������RAM��Ƭѡ�źſ��Ժ�ROM���ã�����ROM��RAM����һ����ַ�ߣ��ڶ�дRAM��ʱ����ȡROM������ͨ������4ѡ1����ѡ��������ֻ���RAM��ROM�е����ݣ������Ϳ�����һ�������źš����У�RAM�Ķ�д�����ź�Ҳ���ص�����ƣ��ɺ�ԭ�е�WR�����źŹ��á���������ʱ��IJִٺ�һ��ʼ������Ʒ���IJ��㣬ʹ��ϵͳ��ƵIJ����������ź����ࡣ��ʹ����ʶ�����Լ���������ơ������ϵIJ��㡣������ǰ����Ʋ���ֺͶ����·ͼ�������IJ��������ں����Ĵ������չ����ʱ���������벻�������ѡ�

��Ȼ���ογ���ƻ���������ֵIJ��㣬��������Ȼ�����dz������̵���ʶ��������EDA������CISC

CPU�����ԭ��������Ҫ���塣

ʮ���������嵥

1.��������״̬�����Ĵ�����Ԫ

�����������������㵥ԪALU�������ݴ�Ĵ�����״̬�����Ĵ�����ɡ����������㵥Ԫ��ִ��������ĿҪ����������㣬������ı�����ʾ���ݴ�Ĵ������ۼ���AC�����ݼĴ���DR��ɣ�״̬�����Ĵ��������ڽ��бȽ�����ʱ�����λ��־��FC/CY�������־��FZ/ZI����

ALU��Ԫ�Ĺ��ܱ�

| S1 |

S0 |

���� |

| 0 |

0 |

��AC��+��DR��������FC��FZ |

| 0 |

1 |

��AC��-��DR��������FC��FZ |

| 1 |

0 |

��AC��-1������FC��FZ |

| 1 |

1 |

80H<=(AC),����FS |

��1��ALU��Ԫ

<pre name="code" class="cpp">LIBRARY

IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ALU IS

PORT(

A:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

S1,S0:IN STD_LOGIC;

BCDOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO

0);

SF,CY,ZI:OUT STD_LOGIC

);

END ALU;

ARCHITECTURE A OF ALU IS

SIGNAL AA,BB,TEMP:STD_LOGIC_VECTOR(8

DOWNTO 0);

BEGIN

PROCESS(S1,S0)

BEGIN

--VARIABLE TEMP1:STD_LOGIC_VECTOR(7

DOWNTO 0);

IF(S1='0' AND S0='0')THEN

AA<='0'&A;

BB<='0'&B;

TEMP<=AA+BB;

BCDOUT<=TEMP(7 DOWNTO 0);

CY<=TEMP(8);

IF(TEMP="100000000")THEN

ZI<='1';

ELSE

ZI<='0';

END IF;

ELSIF(S1='0' AND S0='1')THEN

BCDOUT<=A-B;

IF(A<B)THEN

CY<='1';

ZI<='0';

ELSIF(A=B)THEN

CY<='0';

ZI<='1';

ELSE

CY<='0';

ZI<='0';

END IF;

ELSIF(S1='1' AND S0='0')THEN

AA<='0'&A;

TEMP<=AA+1;

BCDOUT<=TEMP(7 DOWNTO 0);

CY<=TEMP(8);

IF(TEMP="100000000")THEN

ZI<='1';

ELSE

ZI<='0';

END IF;

ELSIF(S1='1' AND S0='1')THEN

--TEMP1="10000000";

BCDOUT<="10000000"-A;

IF("10000000"<=A)THEN

SF<='1';

ELSE

SF<='0';

END IF;

ELSE

BCDOUT<="00000000";

CY<='0';

ZI<='0';

END IF;

END PROCESS;

END A;

��2��״̬�����Ĵ浥ԪLS74

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LS74 IS

PORT(

LDFR:IN STD_LOGIC;

SF,CY,ZI:IN STD_LOGIC;

FS,FC,FZ:OUT STD_LOGIC

);

END LS74;

ARCHITECTURE A OF LS74 IS

BEGIN

PROCESS(LDFR)

BEGIN

IF(LDFR'EVENT AND LDFR='1')THEN

FC<=CY;

FZ<=ZI;

FS<=SF;

END IF;

END PROCESS;

END A;

��3���ݴ�Ĵ�����ԪLS273

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY LS273 IS

PORT(

D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CLK:IN STD_LOGIC;

O:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END LS273;

ARCHITECTURE A OF LS273 IS

BEGIN

PROCESS(CLK)

BEGIN

IF(CLK'EVENT AND CLK='1')THEN

O<=D;

END IF;

END PROCESS;

END A;

2.ͨ�üĴ�����ԪLS273

4��ͨ�üĴ�����R0��R1��R2��R3���Լ�ALU������ⲿ�����ź����±�����ʾ��

| R0_B |

R1_B |

R2_B |

R3_B |

ALU_B |

���� |

| 1 |

1 |

1 |

1 |

0 |

���ALU�Ľ�� |

| 0 |

1 |

1 |

1 |

1 |

�����R0�� |

| 1 |

0 |

1 |

1 |

1 |

�����R1�� |

| 1 |

1 |

0 |

1 |

1 |

�����R2�� |

| 1 |

1 |

1 |

0 |

1 |

�����R3�� |

VHDLԴ����ͬ�ݴ�Ĵ�����ԪLS273

3.��ַ�Ĵ�����ԪLS273

VHDLԴ����ͬ�ݴ�Ĵ�����ԪLS273

4.ָ��Ĵ�����ԪLS273

VHDLԴ����ͬ�ݴ�Ĵ�����ԪLS273

5.1:2������FEN2

1:2������������ALU����������ͨ�üĴ��������ݾ�3ѡ1��·ѡ�����͵��������ߣ����߽�ALU����������ͨ�üĴ�����������������豸��ʾ���������±���ʾ��

| ���� |

��� |

| WR |

LED_B |

X[7..0] |

W1[7..0] |

W2[7..0] |

| 0 |

0 |

�� |

X[7..0] |

| ����ȡֵ |

�� |

X[7..0] |

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FEN2 IS

PORT(

WR,LED_B:IN STD_LOGIC;

X:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

W1,W2:OUT STD_LOGIC_VECTOR(7 DOWNTO

0)

);

END FEN2;

ARCHITECTURE A OF FEN2 IS

BEGIN

PROCESS(LED_B,WR)

BEGIN

IF(LED_B='0' AND WR='0')THEN

W2<=X;

ELSE

W1<=X;

END IF;

END PROCESS;

END A;

6.4ѡ1����ѡ������ԪMUX4

4ѡ1����ѡ������Ԫ�������ⲿ�������ݶ�ID��7..0�ݡ�5ѡ1��·ѡ�����������N1��7..0�ݡ�ֻ���洢��ROM�������ROM[7..0]��RAM�������RAM

[7..0]ѡ��һ��8λ�������ڲ��������ߡ����ܱ������������ʾ��

| ���� |

��� |

| SW_B |

RAM_B |

ROM_B |

ID[7..0] |

ROM [7..0] |

N2[7..0] |

EW[7..0] |

| 0 |

�� |

�� |

�� |

�� |

�� |

ID[7..0] |

| 1 |

�� |

0 |

�� |

�� |

�� |

ROM[7..0] |

| 1 |

1 |

1 |

�� |

�� |

�� |

N1[7..0] |

| 1 |

0 |

1 |

�� |

�� |

�� |

RAM[7..0] |

MUX4��VHDLԴ��������

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MUX4 IS

PORT(

ID:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

RAM_B,SW_B,ROM_B:IN STD_LOGIC;

N1,ROM,RAM:IN STD_LOGIC_VECTOR(7 DOWNTO

0);

EW:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END MUX4;

ARCHITECTURE A OF MUX4 IS

BEGIN

PROCESS(SW_B,RAM_B,ROM_B)

BEGIN

IF(SW_B='0')THEN

EW<=ID;

ELSIF(RAM_B='0')THEN

EW<=RAM;

ELSIF(ROM_B='0')THEN

EW<=ROM;

ELSE

EW<=N1;

END IF;

END PROCESS;

END A;

7.5ѡ1����ѡ������ԪMUX5

MUX5�������ĸ�ͨ�üĴ�������������˺�ALU�����������ѡ��һ��8λ�����ݽ���1:2����������������ˡ����ܱ����±�����ʾ��

| ��������ź� |

��� |

| C |

D |

E |

F |

G |

W[7..0] |

| 0 |

1 |

1 |

1 |

1 |

X1[7..0] |

| 1 |

0 |

1 |

1 |

1 |

X2[7..0] |

| 1 |

1 |

0 |

1 |

1 |

X3[7..0] |

| 1 |

1 |

1 |

0 |

1 |

X4[7..0] |

| 1 |

1 |

1 |

1 |

0 |

X5[7..0] |

MUX5��VHDLԴ�������£�

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MUX5 IS

PORT(

C,D,E,F,G:IN STD_LOGIC;

X1,X2,X3,X4,X5:IN STD_LOGIC_VECTOR(7

DOWNTO 0);

W:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END MUX5;

ARCHITECTURE A OF MUX5 IS

SIGNAL SEL:STD_LOGIC_VECTOR(4 DOWNTO

0);

BEGIN

SEL<=G&F&E&D&C;

PROCESS(SEL)

BEGIN

IF(SEL="11110")THEN

W<=X1;

ELSIF(SEL="11101")THEN

W<=X2;

ELSIF(SEL="11011")THEN

W<=X3;

ELSIF(SEL="10111")THEN

W<=X4;

ELSIF(SEL="01111")THEN

W<=X5;

ELSE

NULL;

END IF;

END PROCESS;

END A;

8.�����������ԪPC

�����������Ԫ���ڿ����źŵĿ����¾����塰0�����ü�����ֵ�ͼ�1�Ĺ��ܣ������DZ�֤�����˳��ִ�У���ִ����תָ��ʱ��ͨ����PCֵ�Դﵽ����ת�Ʒ�֧��Ŀ�ġ����ܱ������������ʾ��

PC�������������Ԫ�����ܱ�

| CLR |

LOAD |

LDPC |

���� |

| 0 |

�� |

�� |

��PC��0 |

| 1 |

0 |

�� |

BUS-->PC |

| 1 |

1 |

0 |

��װ��Ҳ������ |

| 1 |

1 |

�� |

PC+1 |

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY PC IS

PORT(

LOAD,LDPC,CLR:IN STD_LOGIC;

D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

O:OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END PC;

ARCHITECTURE A OF PC IS

SIGNAL QOUT:STD_LOGIC_VECTOR(7 DOWNTO

0);

BEGIN

PROCESS(LDPC,CLR,LOAD)

BEGIN

IF(CLR='0')THEN

QOUT<="00000000";

ELSIF(LDPC'EVENT AND LDPC='1')THEN

IF(LOAD='0')THEN

QOUT<=D;--BUS->PC

ELSE

QOUT<=QOUT+1;--PC=PC+1

END IF;

END IF;

END PROCESS;

O<=QOUT;

END A;

9.���洢����ԪROM

���洢����Ԫ�������CPUҪ���еij�������ݣ��Ǽ����ϵͳ�бز����ٵ���Ҫ��ɲ��֡��书�ܱ�������ı�����ʾ��

���洢��ROM���ܱ�

ROM��VHDLԴ�������£�

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ROM IS

PORT(

CS:IN STD_LOGIC;

DOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO

0);

ADDR:IN STD_LOGIC_VECTOR(7 DOWNTO

0)

);

END ROM;

ARCHITECTURE A OF ROM IS

BEGIN

PROCESS(CS)

BEGIN

IF (CS'EVENT AND CS='0')THEN

CASE ADDR IS

WHEN "00000000" => DOUT<="01110000";--

MOV R0,1

WHEN "00000001" => DOUT<="00000001";

WHEN "00000010" => DOUT<="01110001";--

MOV R1,11

WHEN "00000011" => DOUT<="00001011";

WHEN "00000100" => DOUT<="01100011";--L1:IN1

R3

WHEN "00000101" => DOUT<="10011100";--

MOV2 R3,[R0]

WHEN "00000110" => DOUT<="11010000";--

INC R0

WHEN "00000111" => DOUT<="10100001";--

CMP R0,R1

WHEN "00001000" => DOUT<="10110000";--

JB L1

WHEN "00001001" => DOUT<="00000100";

WHEN "00001010" => DOUT<="01110000";--

MOV R0,1

WHEN "00001011" => DOUT<="00000001";

WHEN "00001100" => DOUT<="01110001";--

MOV R1,11

WHEN "00001101" => DOUT<="00001011";

WHEN "00001110" => DOUT<="01110010";--

MOV R2,FF

WHEN "00001111" => DOUT<="11111111";

WHEN "00010000" => DOUT<="10000011";--L2:MOV1

[R0],R3

WHEN "00010001" => DOUT<="11010000";--

INC R0

WHEN "00010010" => DOUT<="10100100";--

CMP R1,R0

WHEN "00010011" => DOUT<="10110000";--

JB L5

WHEN "00010100" => DOUT<="00100010";

WHEN "00010101" => DOUT<="01000011";--

TEST R3

WHEN "00010110" => DOUT<="11000000";--

JN L3

WHEN "00010111" => DOUT<="00011010";

WHEN "00011000" => DOUT<="11100000";--

JMP L2

WHEN "00011001" => DOUT<="00010000";

WHEN "00011010" => DOUT<="10101110";--L3:CMP

R3,R2

WHEN "00011011" => DOUT<="10110000";--

JB L4

WHEN "00011100" => DOUT<="00011111";

WHEN "00011101" => DOUT<="11100000";--

JMP L2

WHEN "00011110" => DOUT<="00010000";

WHEN "00011111" => DOUT<="01011110";--L4:MOV3

R3,R2

WHEN "00100000" => DOUT<="11100000";--

JMP L2

WHEN "00100001" => DOUT<="00010000";

WHEN "00100010" => DOUT<="11111000";--L5:OUT1

R2

WHEN "00100011" => DOUT<="11100000";--

JMP L5

WHEN "00100100" => DOUT<="00100010";

WHEN OTHERS => NULL;

END CASE;

END IF;

END PROCESS;

END A;

10.ʱ���������ԪCOUNTER

COUNTER�����������������źţ�T1��T2��T3��T4�����Ը��ֿ����ź�ʵʩʱ���ϵĿ��ơ��书�ܱ�������ı�����ʾ��

| ���� |

��� |

��ע |

| Q |

CLR |

T1 |

T2 |

T3 |

T4 |

��CLR��Ϊ1��Q���ϱ��ص���ʱ��T1Ϊ��1����T2��T4Ϊ��0�� |

| �� |

0 |

0 |

0 |

0 |

0 |

| �� |

1 |

ѭ������1�� |

COUNTER��VHDLԴ�������£�

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNTER IS

PORT(

Q,CLR:IN STD_LOGIC;

T2,T3,T4:OUT STD_LOGIC

);

END COUNTER;

ARCHITECTURE A OF COUNTER IS

SIGNAL X:STD_LOGIC_VECTOR(1 DOWNTO 0);

BEGIN

PROCESS(Q,CLR)

BEGIN

IF(CLR='0')THEN

T2<='0';

T3<='0';

T4<='0';

X<="00";

ELSIF(Q'EVENT AND Q='1')THEN

X<=X+1;

T2<=(NOT X(1)) AND X(0);

T3<=X(1) AND (NOT X(0));

T4<=X(1) AND X(0);

END IF;

END PROCESS;

END A;

11.�������Ƶ�ԪCROM

�����������Ҫ�ɵ�ַת������·ADDR����ַ�Ĵ���aa�����ƴ洢��CONTEROM������Ĵ���MCOMMAND�ȼ�������ɡ�Ϊ�����·����������ߣ��ڽ������ʱ��������F1��F2��F3���������ڶ������������֮��ת������������������VHDLԴ�������£�

��1����ַת������·ADDR

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY ADDR IS

PORT(

I7,I6,I5,I4:IN STD_LOGIC;

FS,FZ,FC,T4,P1,P2,P3:IN STD_LOGIC;

SE6,SE5,SE4,SE3,SE2,SE1:OUT STD_LOGIC

);

END ADDR;

ARCHITECTURE A OF ADDR IS

BEGIN

SE6<=NOT(NOT FS AND P3 AND T4);

SE5<=NOT((NOT FC OR FZ)AND P2 AND

T4);

SE4<=NOT(I7 AND P1 AND T4);

SE3<=NOT(I6 AND P1 AND T4);

SE2<=NOT(I5 AND P1 AND T4);

SE1<=NOT(I4 AND P1 AND T4);

END A;

��2����ַ�Ĵ���aa

��ַ�Ĵ����ڲ���Ҫ��6��MMM������ɣ��ٽ�����Ӧ�����롢����źţ�VHDLԴ�������£�

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY MMM IS

PORT(

SE:IN STD_LOGIC;

T2:IN STD_LOGIC;

D:IN STD_LOGIC;

CLR:IN STD_LOGIC;

UA:OUT STD_LOGIC

);

END MMM;

ARCHITECTURE A OF MMM IS

BEGIN

PROCESS(CLR,SE,T2)

BEGIN

IF(CLR='0')THEN

UA<='0';

ELSIF(SE='0')THEN

UA<='1';

ELSIF(T2'EVENT AND T2='1')THEN

UA<=D;

END IF;

END PROCESS;

END A;

(3)��ַת����F1

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY F1 IS

PORT(

UA5,UA4,UA3,UA2,UA1,UA0:IN STD_LOGIC;

D:OUT STD_LOGIC_VECTOR(5 DOWNTO 0)

);

END F1;

ARCHITECTURE A OF F1 IS

BEGIN

D(5)<=UA5;

D(4)<=UA4;

D(3)<=UA3;

D(2)<=UA2;

D(1)<=UA1;

D(0)<=UA0;

END A;

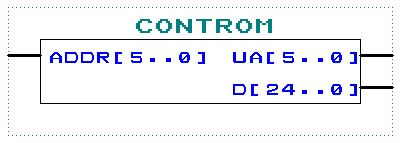

(4�����ƴ洢��CONTEROM

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CONTROM IS

PORT(

ADDR:IN STD_LOGIC_VECTOR(5

DOWNTO 0);

UA:OUT STD_LOGIC_VECTOR(5 DOWNTO 0);

D:OUT STD_LOGIC_VECTOR(24 DOWNTO 0)

);

END CONTROM;

ARCHITECTURE A OF CONTROM IS

SIGNAL DATAOUT:STD_LOGIC_VECTOR(30 DOWNTO

0);

BEGIN

PROCESS(ADDR)

BEGIN

CASE ADDR IS

WHEN "000000"=>DATAOUT<="1100111100110010011110000000001";

WHEN "000001"=>DATAOUT<="1100110010110010010110100010000";

WHEN "000010"=>DATAOUT<="1100110001110010010110000000000";

WHEN "000011"=>DATAOUT<="0010110001110010011110000000000";

WHEN "000100"=>DATAOUT<="1000110000100010011110000000000";

WHEN "000101"=>DATAOUT<="1100110000010010111110000000110";

WHEN "000110"=>DATAOUT<="1100110000110110011111000000000";

WHEN "000111"=>DATAOUT<="1100110001111000011110000000000";

WHEN "001000"=>DATAOUT<="1100101000110010010110000000000";

WHEN "001001"=>DATAOUT<="1000110000110010011110000000000";--9

WHEN "010001"=>DATAOUT<="1010101000110010010110000000000";--11

WHEN "010010"=>DATAOUT<="1100110000110010011110000000011";--12

WHEN "010011"=>DATAOUT<="1100110000111110011111000000000";--13

WHEN "010100"=>DATAOUT<="1100110000010011011110000010011";--14TEST

Rd

WHEN "010101"=>DATAOUT<="1100110001100010011110000000000";--15

MOV3 Rs>Rd

WHEN "010110"=>DATAOUT<="1100110001110010011010000000000";--16

IN1 RD

WHEN "010111"=>DATAOUT<="1100111100110010011110000000010";--17

MOV RD #DATA

WHEN "011000"=>DATAOUT<="1101010100100010011110000000011";--18

MOV1 [Rs]>Rd

WHEN "011001"=>DATAOUT<="1101010100010010011110000000100";--19

MOV2 [Rs]<Rd

WHEN "011010"=>DATAOUT<="1100110000100011011110000000101";--1A

CMP Rs Rd

WHEN "011011"=>DATAOUT<="1100111100110010011110010100000";--1B

JB

WHEN "011100"=>DATAOUT<="1100111100110010011110011010001";--1C

JN

WHEN "011101"=>DATAOUT<="1100110000010011011110000000111";--1D

INC Rd

WHEN "011110"=>DATAOUT<="1100111100110010011110000001000";--1E

JMP

WHEN "011111"=>DATAOUT<="1100110000100010001100000000000";--1F

OUT Rs

WHEN "100000"=>DATAOUT<="1010101000110010010110000000000";

WHEN "110000"=>DATAOUT<="1100110000110010011110000000000";

WHEN "110001"=>DATAOUT<="1100110000110010011110000000000";

WHEN OTHERS =>DATAOUT<="1100110000110010011110000000000";

END CASE;

UA(5 DOWNTO 0)<=DATAOUT(5 DOWNTO

0);

D(24 DOWNTO 0)<=DATAOUT(30 DOWNTO

6);

END PROCESS;

END A;

(5)����Ĵ���MCOMMAND

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY MCOMMAND IS

PORT(

T2,T3,T4,I3,I2,I1,I0:IN STD_LOGIC;

O:IN STD_LOGIC_VECTOR(24 DOWNTO 0);

P1,P2,P3,RAM_B,WR1,CS1,PC,ADDR,LOAD,LDPC,LDAR,LDIR,LDR0,LDR1,LDR2,LDR3,R0_B,R1_B,R2_B,R3_B,S1,S0,ALU_B,LDAC,

LDDR,WR,CS,SW_B,LED_B,LDFR:OUT STD_LOGIC

);

END MCOMMAND ;

ARCHITECTURE A OF MCOMMAND IS

SIGNAL DATAOUT:STD_LOGIC_VECTOR(24 DOWNTO

0);

BEGIN

PROCESS(T2)

BEGIN

IF(T2'EVENT AND T2='1')THEN

DATAOUT(24 DOWNTO 0)<=O(24 DOWNTO

0);

END IF;

P3<=DATAOUT(0);

P2<=DATAOUT(1);

P1<=DATAOUT(2);

LDFR<=DATAOUT(3) AND T4;

LED_B<=DATAOUT(4);

SW_B<=DATAOUT(5);

CS<=DATAOUT(6);

WR<=DATAOUT(7)OR(NOT T3);

LDDR<=DATAOUT(8) AND T4;

LDAC<=DATAOUT(9) AND T4;

ALU_B<=DATAOUT(10);

S0<=DATAOUT(11);

S1<=DATAOUT(12);

R3_B<=(DATAOUT(14) OR (NOT I1)

OR (NOT I0))AND (DATAOUT(13) OR (NOT I3 ) OR (NOT I2));

R2_B<=(DATAOUT(14) OR (NOT I1)

OR I0)AND (DATAOUT(13) OR (NOT I3 ) OR I2);

R1_B<=(DATAOUT(14) OR I1 OR (NOT

I0))AND (DATAOUT(13) OR I3 OR (NOT I2));

R0_B<=(DATAOUT(14) OR I1 OR I0)AND

(DATAOUT(13) OR I3 OR I2);

LDR3<=T4 AND DATAOUT(15) AND I1

AND I0;

LDR2<=T4 AND DATAOUT(15) AND I1

AND (NOT I0);

LDR1<=T4 AND DATAOUT(15) AND (NOT

I1) AND I0;

LDR0<=T4 AND DATAOUT(15) AND (NOT

I1) AND (NOT I0);

LDIR<=DATAOUT(16) AND T3;

LDAR<=DATAOUT(17) AND T3;

LDPC<=DATAOUT(18) AND T4;

LOAD<=DATAOUT(19);

PC<=DATAOUT(20);

ADDR<=DATAOUT(21);

WR1<=DATAOUT(22)OR (NOT(T2 OR T3));

CS1<=DATAOUT(23)OR (NOT T3);

RAM_B<=DATAOUT(24);

END PROCESS;

END A;

(6)��ַת����F2

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY F2 IS

PORT(

D:IN STD_LOGIC_VECTOR(5 DOWNTO 0);

UA5,UA4,UA3,UA2,UA1,UA0:OUT STD_LOGIC

);

END F2;

ARCHITECTURE A OF F2 IS

BEGIN

UA5<=D(5);

UA4<=D(4);

UA3<=D(3);

UA2<=D(2);

UA1<=D(1);

UA0<=D(0);

END A;

(7)ָ�����ת����F3

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY F3 IS

PORT(

D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);

UA7,UA6,UA5,UA4,UA3,UA2,UA1,UA0:OUT

STD_LOGIC

);

END F3;

ARCHITECTURE A OF F3 IS

BEGIN

UA7<=D(7);

UA6<=D(6);

UA5<=D(5);

UA4<=D(4);

UA3<=D(3);

UA2<=D(2);

UA1<=D(1);

UA0<=D(0);

END A;

|