| ±ύΦ≠ΆΤΦω: |

±ΨΈΡ÷ς“ΣΫι…ή3Ηω≤ΩΖ÷ΘΚ¥”Verilog

HDLΒΡάύ–ΆΚΆ≥ΘΝΩΒΫ”≤ΦΰΒΡ”≥…δΘΜ¥”Verilog”οΨδΒΫ”≤Φΰ¬ΏΦ≠Ο≈ΒΡ”≥…δΘ§Ϋβ ΆΝΥ‘ΥΥψΖϊΓΔ±μ¥ο ΫΚΆΗ≥÷Β”οΨδ «»γΚΈ”≥…δ≥…”≤ΦΰΒΡΘΜ“‘ΉέΚœΈΣΡΩ±ξΕ‘”≤Φΰ‘ΣΦΰΫχ––Ϋ®ΡΘΘ§≤Δ«“≤…”ΟVerilog

HDLΫχ–– Βœ÷Θ®Ϋ®ΡΘΒΡ ΨάΐΘ©ΓΘ

±ΨΈΡά¥Ή‘”ΎCSDNΘ§”…ΜπΝζΙϊ»μΦΰAlice±ύΦ≠ΓΔΆΤΦωΓΘ |

|

1. Ϋι…ή

1.1 ≤Ο¥ «ΉέΚœΘΩ

Verilog HDLΜρVHDLΕΦ÷Μ «“Μ÷÷”≤ΦΰΒΡΟη ω”ο―‘Θ§≤Δ«“‘ –μ‘Ύ≤ΜΆ§ΒΡ≥ιœσ≤ψ¥Έ…œΕ‘Βγ¬ΖΫχ––Ϋ®ΡΘΓΘVerilogHDL≤ύ÷Ί”ΎΒγ¬ΖΦΕΘ§Ω…“‘‘ΎΟ≈ΦΕΚΆΦΡ¥φΤς¥Ϊ δΦΕΘ®RTLΘ©Οη ω”≤ΦΰΘ§“≤Ω…“‘‘ΎΥψΖ®ΦΕΕ‘”≤ΦΰΦ”“‘Οη ωΓΘΕχVHDL≤ύ÷Ί”ΎœΒΆ≥ΦΕΓΘ

ΉέΚœΨΆ «ΫΪVerilogΟη ωΒΡRTLΦΕΒΡΒγ¬ΖΡΘ–ΆΙΙ‘λ≥ωΟ≈ΦΕΆχ±μΒΡΙΐ≥ΧΓΘΉέΚœ÷Μ «Ηω÷–Φδ≤Ϋ÷ηΘ§ΉέΚœΚσ…ζ≥…ΒΡΆχ±μΈΡΦΰΘ§ΨΆ «”…ΒΦœΏœύΜΞΝ§Ϋ”ΒΡΦΡ¥φΤς¥Ϊ δΦΕΙΠΡήΩι

Θ®œώ «¥ΞΖΔΤςΓΔΥψ θ¬ΏΦ≠ΒΞ‘ΣΚΆΕύ¬Ζ―Γ‘ώΤςΒ»Θ©Ήι≥…ΒΡΓΘ’βάοΨΆ–η“Σ“ΜΗωΫ–ΉωRTLΡΘΩιΙΙ‘λΤςΒΡ≥Χ–ρΘ§”Οά¥’κΕ‘”ΟΜß÷ΗΕ®ΒΡΡΩ±ξΙΛ“’¥”‘ΛΕ®“ε‘ΣΦΰΩβ÷–ΙΙ‘λΜρΜώ»ΓΟΩ“ΜΗω±Ί–κΒΡRTLΙΠΡήΡΘΩιΓΘ

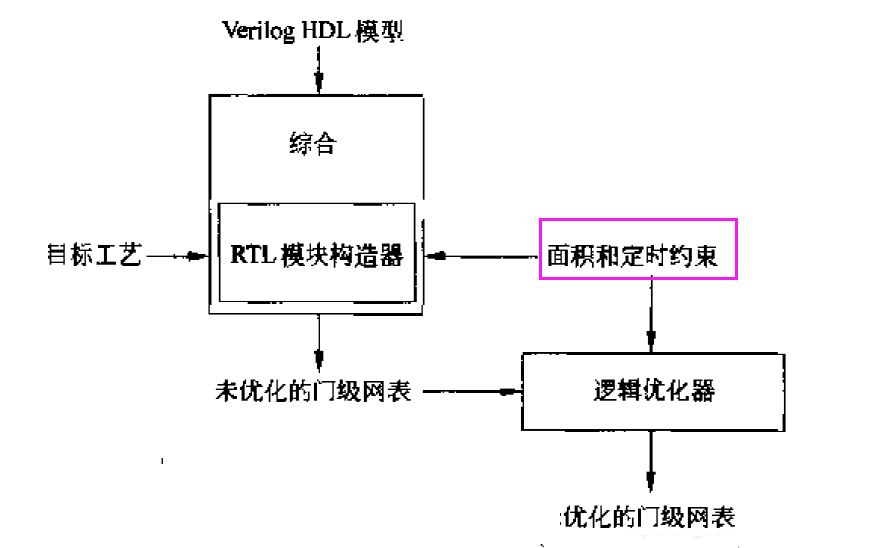

ΆΦ1 ΘΚΉέΚœΙΐ≥Χ

ΉέΚœ≤ζ…ζΆχ±μΈΡΦΰΚσΘ§¬ΏΦ≠”≈Μ·Τς ΜαΕΝ»κΆχ±μΘ§≤Δ«“ΜαΑ¥’’”ΟΜßΧαΙ©ΒΡΟφΜΐΘ®Φ¥Ή ‘¥“Σ«σΘ©ΚΆΕ® ±Θ® ±–ρ“Σ«σΘ©‘Φ χΈΣΡΩ±ξά¥”≈Μ·Άχ±μΓΘ≤Δ«“Θ§’β–©ΟφΜΐΚΆΕ® ±‘Φ χ“≤ΡήΙΜ÷ΗΒΦ

ΡΘΩιΙΙ‘λΤς «ΓΒ±ΒΊ―Γ»ΓΜρ…ζ≥…ΦΡ¥φΤς¥Ϊ δΦΕΙΠΡήΩιΓΘ

1.2 ≤ΜΩ…ΉέΚœ

…œΈΡΫι…ήΝΥHDLΒΡΟη ω”–≤ΜΆ§ΒΡ≥ιœσ≤ψ¥ΈΘ§¥”Ο≈ΦΕΓΔRTLΦΕΓΔ––ΈΣΦΕ“‘ΦΑΥψΖ®ΦΕΫχ––Ϋ®ΡΘΓΘΒΪ «Θ§≤Δ≤Μ «Υυ”–≤ψ¥Έ…œΒΡΟη ωΖΫ ΫΕΦΩ…“‘±ΜΉέΚœ≥…œκ“ΣΒΡ”≤Φΰ‘ΣΦΰΘ§Φ¥≤ΜΩ…ΉέΚœΓΘ±»»γVerilog÷–¥φ‘Ύ“Μ–©”Ο”ΎΖ¬’φ―ι÷ΛΒΡΉ”Φ·Θ§ τ”ΎΖ¬’φ―ι÷Λ”ο―‘Θ§÷Μ‘ΎΖ¬’φ ±Κρ Ι”ΟΘ§≤ΜΡή±ΜΉέΚœ≥…Βγ¬ΖΘ§“ρΈΣΟΜ”–œύ”ΠΒΡ”≤Φΰ‘ΣΦΰ”κΤδΕ‘”ΠΓΘ»γœΒΆ≥»ΈΈώ$dsiplay(),

initial”οΨδΒ»ΓΘ

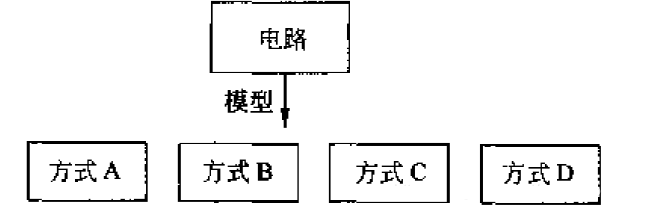

ΜΙ–η“ΣΥΒΟςΒΡ «Θ§≤ΜΆ§ΒΡΉέΚœΤςΥυ÷ß≥÷ΒΡVerilogΩ…ΉέΚœΒΡΉ”Φ·“ΜΑψ «≤ΜΆ§ΒΡΘ§ΕχVerilog÷–≤Μ¥φ‘ΎΒΞΗωΒΡΕ‘œσά¥±μ ΨΥχ¥φΤςΜρ¥ΞΖΔΤς“ρ¥ΥΟΩ“Μ÷÷ΉέΚœΤςΕΦΜα”–Ή‘ΦΚΒΡΉέΚœΜζ÷Τά¥ Βœ÷Υχ¥φΤςΜρ¥ΞΖΔΤςΒΡΫ®ΡΘΓΘœ¬ΆΦΥΒΟςΝΥVerilog÷–≤…”Ο≤ΜΆ§ΒΡΟη ωΖΫ Ϋ»ΞΟη ωΆ§“ΜΗωΒγ¬ΖΓΘΒΪΡ≥ΉέΚœœΒΆ≥ΫωΫω÷ß≥÷ΖΫ ΫAΚΆBΘ§»¥≤Μ÷ß≥÷ΖΫ ΫCΘ§’β“≤ΥΒΟςΆ§“ΜΗωΒγ¬ΖΡΘΩιΘ§‘Ύ≤ΜΆ§ΒΡΉέΚœΤς÷°Φδ“ΜΑψ «≤ΜΩ…“Τ÷≤ΒΡΓΘΕΰΖΫ ΫD τ”Ύ―ΙΗυΨΆ≤ΜΩ…ΉέΚœΒΡ“Μ÷÷ΓΘ

ΆΦ2 ΘΚΆ§―υΒΡ––ΈΣΘ§”–≤ΜΆ§ΒΡΫ®ΡΘΖΫ Ϋ

1.3 ‘Ύ…ηΦΤΝς≥Χ÷–ΒΡΈΜ÷ΟΘΩ

≤ΜΆ§ΉέΚœΤς÷ß≥÷ΒΡΉέΚœΉ”Φ·≤ΜΆ§Θ§’βΨΆΈΣΩΣΖΔ»Υ‘±¥χά¥ΒΡάß»≈ΓΘ‘Ύ―ßœΑΚΆ Ι”ΟΒΡΙΐ≥Χ÷–Θ§≤ΜΫω“ΣάμΫβVerilogΓΓHDLΕχ«“ΜΙΒΟάμΫβΧΊΕ®ΉέΚœΤςΒΡΫ®ΡΘΖΫ ΫΘ§’β―υ≤≈Ω…–¥»κΆξ»ΪΩ…ΉέΚœΒΡΡΘ–ΆΓΘœ¬Οφ «FPGAΩΣΖΔ ±ΒΡΒδ–ΆΝς≥ΧΘ§ΒΪ≤ΔΖ«ΙΧΕ®ΓΘ

ΆΦ3ΘΚΒδ–ΆΒΡ…ηΦΤΝς≥Χ

2. ”≥…δΜζ÷Τ

Φ»»ΜΉέΚœΤςΡήΙΜΫΪHDL”ο―‘ΉΣΜΜ≥…Ο≈ΦΕΆχ±μΘ§Ρ«Ο¥ΉέΚœΤς±ΊΕ®”–“Μ÷÷”≥…δΒΡΜζ÷ΤΘ§ΡήΙΜ Βœ÷Verliog¥ζ¬κ÷–ΒΡΡ≥–©±δΝΩΓΔΉιΦΰ”≥…δ≥…Ε‘”ΠΒΡ”≤Φΰ‘ΣΦΰΓΘ

ΆΦ4ΘΚΉέΚœΙΐ≥Χ…φΦΑΒΫΒΡΝΫΗωΝλ”ρ

Part1 -¥”Verilog HDLΒΡάύ–ΆΚΆ≥ΘΝΩΒΫ”≤ΦΰΒΡ”≥…δ

÷ς“ΣΫι…ή Verilog HDLΒΡάύ–ΆΚΆ≥ΘΝΩΒΫ”≤ΦΰΒΡ”≥…δΓΘ

1. ¬ΏΦ≠÷ΒΧεœΒ

”≤ΦΰΫ®ΡΘ≥Θ”ΟΒΡ÷ΒΘΚ¬ΏΦ≠ΘΑΓΔ¬ΏΦ≠1ΓΔΗΏΉηΩΙΓΔΈόΙΊ÷ΒΓΔ≤ΜΕ®÷°ΓΘ‘ΎVerilog÷–Ε‘ΈόΙΊ÷Β÷°ΆβΒΡΤδΥϊ÷ΒΕΦΉωΝΥΟς»ΖΒΡΕ®“εΘ§Β±÷Β

x ±ΜΗ≥÷ΒΗχΡ≥“ΜΗω±δΝΩ ±Θ§ΉέΚœΤςΜαΫΪΗΟ÷Β ”ΈΣ ΈόΙΊ÷Β ΓΘΕ‘”ΠΙΊœΒΘΚ

ΆΦ5ΘΚVerilog HDL ΐ÷Β”κ”≤ΦΰΫ®ΡΘ÷°ΦδΕ‘”ΠΙΊœΒ

1.1 ΈΜΩμ

1Θ© ±δΝΩ ΐΨίάύ–Ά

ΐΨίάύ–ΆΘ®Data Type Θ© «”Οά¥Ζ÷±π±μ Ψ ΐΉ÷Βγ¬Ζ÷–ΒΡΈοάμΝ§œΏΓΔ ΐΨί¥φ¥ΔΚΆ¥Ϊ δΒΞ‘ΣΒ»ΈοάμΝΩΒΡΓΘ

Verilog÷–ΒΡ±δΝΩ ΐΨίάύ–Ά”–ΝΫ÷÷ ΘΚ a) ΦΡ¥φΤς ΐΨίάύ–Ά ΚΆ

b) ΆχœΏ ΐΨίάύ–Ά Θ®net–ΆΘ©ΓΘ

‘ΎVerilog1995÷–ΦΡ¥φΤςάύ–ΆΘ§ΒΪ‘ΎVerilog2001±ξΉΦ÷–ΫΪregister“Μ¥ΈΗΡΈΣΝΥvariableΘ§“‘±ήΟβ≥θ―ß’ΏΫΪregisterΚΆ”≤Φΰ÷–ΒΡΦΡ¥φΤςΗ≈ΡνΜλœΐΓΘ

a) ΆχœΏ ΐΨίάύ–Ά

‘Ύ…υΟς ± Ω…“‘Ος»ΖΒΡ÷ΗΕ®±δΝΩΒΡΈΜΩμΓΘΈ¥Ος»Ζ÷ΗΟςΘ§Ρ§»œ1ΈΜΓΘΡήΙΜΉέΚœΒΡΆχœΏ ΐΨίάύ–Ά”–ΘΚ

wire [5:0] data_bus

; //6ΈΜΒΡwireΆχœΏ

wor Ax ; //1ΈΜworΆχœΏ |

wireΆχœΏ «ΉνΉν≥Θ”ΟΒΡάύ–ΆΘ§Β±ΕύΗω«ΐΕ·‘¥«ΐΕ·Ά§“ΜΗυwireΆχœΏ ±Θ§’β–©«ΐΕ·‘¥ΒΡ δ≥ωΕΥΨΆΜα±ΜΕΧΫ”‘Ύ“ΜΤπΘ®œΏ”κΘ©ΘΚ

module wire_example(BpW

,Error , Wait, Vaild , Clear);

input Error, Wait, Valid, Clear;

output BpW;

wire Bpw;

assign BpW = Error & Wait ;

assign BpW = Error | Clear;

endmodule |

»γΆΦ6Υυ Ψ

ΆΦ6ΘΚΕύ«ΐΕ·‘¥«ΐΕ·Ά§“ΜwireΆχœΏ

Β±≤…”ΟΓΑΜρ¬ΏΦ≠ΚΆΓΑ”κ¬ΏΦ≠Γ± Βœ÷ΕύΗω«ΐΕ·‘¥«ΐΕ·Ά§“ΜΗυΆχœΏΒΡ«ΐΕ·–ßΙϊ

Θ§‘ρΖ÷±π–η“Σ”ΟworΚΆwandΆχœΏάύ–ΆΓΘΉέΚœΒΡ ±ΚρΘ§Ά§“ΜΗυworΆχœΏΒΡΕύΗω«ΐΕ·‘¥ΕΦΝ§Ϋ”ΒΫ“ΜΜρΟ≈…œΘ§Εχ«ΐΕ·Ά§“ΜΗυwangΆχœΏΒΡ«ΐΕ·‘¥ΕΦΝ§Ϋ”ΒΫ”κΟ≈…œΓΘ Ψάΐ»γœ¬ΘΚ

module UseGates(BpW,

Bpr,ValidȧError,Wait,Clear);

input Error,Wait,Clear;

output BpW,BpR;

wor BpW;

wand BpRΘΜ

assign BpW = Error & Wait ;

assign BPW = Valid | Clear;

assign BpR = Error ^Valid;

assign BpR = !clear;

endmodule |

ΉέΚœΚσΒΡΆχ±μ»γœ¬ΆΦ7Υυ ΨΘΚ

ΆΦ7ΘΚΕύΗω«ΐΕ·‘¥«ΐΕ·worΆχœΏΚΆwandΆχœΏ

triΆχœΏ–Ά”κwireΆχœΏ–Ά≤…”ΟœύΆ§ΒΡΖΫ ΫΉέΚœΓΘΕχsupply0ΆχœΏΉέΚœΒΡΝ§œΏΜαΙΧΕ®Ν§Ϋ”‘Ύ0ΒγΤΫΘ®¬ΏΦ≠0Θ©…œΘ§Εχ”…supply1ΆχœΏΉέΚœ≥ωΒΡΝ§œΏΙΧΕ®Ν§Ϋ”‘Ύ1ΒγΤΫΘ®¬ΏΦ≠1Θ©…œΓΘ

b) ΦΡ¥φΤς ΐΨίάύ–ΆΘ®Variable–ΆΘ©

Ω…ΉέΚœΒΡΦΡ¥φΤςάύ–Ά”–ΘΚreg –Ά ΚΆ integer–Ά ΓΘ

reg–Ά…υΟς”οΨδΆ§―υΩ…“‘Ος»ΖΒΊ÷ΗΕ®ΈΜΩμΘ§Φ¥ΗΟ±δΝΩ‘Ύ”≤Φΰ…œœύ”ΠΒΡΈΜ ΐΘ§Έ¥÷ΗΕ®Ρ§»œ1bitΓΘΕχ’ϊ ΐάύ–ΆΉν¥σΈΜΩμ32bitΘ§≤Δ«“ΦΌΕ®”ΟΕΰΫχ÷Τ≤Ι¬κ–Έ Ϋ±μ ΨΘ§Φ¥ «”–ΖϊΚ≈ ΐ–Έ ΫΓΘ

Integer–Ά

Εύ”Ο”Ύ―≠ΜΖ±δΝΩ ΘΜ

≤ΜΡήΉςΈΣΈΜœρΝΩΖΟΈ ΘΜ

ΉέΚœ ±Θ§integer–Ά±δΝΩΒΡ≥θ Φ÷ΒΈΜxΓΘ

‘Ύ…υΟς’ϊ ΐ–Ά±δΝΩ ±Θ§Ω…“‘»ΟΉέΚœΤςΉ‘ΦΚΕ‘ ΐΨίΝςΖ÷Έωά¥»ΖΕ®Ης’ϊ–Ά±δΝΩΥυ–ηΒΡΉν¥σΈΜΩμΓΘάΐ»γΘΚ

wire [4ΘΚ0] AΘ§BΘΜ

integer SumΘΜ

...

sum = A + B ; |

Ω…“‘»ΖΕ®’βάοΒΡSumΈΜΩμ”ΠΗΟΈΣ6ΈΜΘ§Ι “ΜΗω6ΈΜΒΡΦ”Ζ®ΤςΨΆΙΜΝΥΘ§≤Δ«“SumΒΡΉνΗΏΈΜΈΣΫχΈΜΈΜΓΘ

timeΚΆreal–Ά“≤ τ”ΎΦΡ¥φΤςάύ–ΆΘ§ΒΪ «≤ΜΡήΉέΚœΓΘ

2Θ©≥ΘΝΩ

Verilog÷–”–3÷÷≥ΘΝΩΘΚ

’ϊ–ΆΘ®integerΘ© ΘΜ

Β–ΆΘ®realΘ© ΘΜ

Ή÷Ζϊ¥°–ΆΘ®stringsΘ©ΓΘ

Τδ÷–Θ§ Β–ΆΚΆΉ÷Ζϊ¥°–ΆΒΡ≥ΘΝΩ≤Δ≤ΜΡήΙΜ±ΜΉέΚœΘ§Εχ’ϊ–Ά «Ω…“‘ΉέΚœΒΡΓΘ

’ϊ–Ά

’ϊ–Ά≥ΘΝΩΒΡ±μ ΨΘΚ a) ΦρΒΞΒΡ °Ϋχ÷Τ b)Μυ ΐΗώ Ϋ ΓΘ

–η“ΣΉΔ“βΘΚ

Β ΐ–ΆΘ®RealΘ©

Β ΐ”–ΝΫ÷÷±μ ΨΖΫΖ®ΘΚ aΘ© °Ϋχ÷Τ±μ ΨΖ® b) ΩΤ―ßΦΤ ΐΖ®

Ή÷Ζϊ¥°Θ®StringsΘ©

Ή÷Ζϊ¥° «ΥΪ“ΐΚ≈ΡΎΒΡΉ÷Ζϊ–ρΝ–ΘΜ

Ή÷Ζϊ–ρΝ–≤ΜΡήΖ÷≥…Εύ–– ι–¥Θ§άΐ»γΘΚ "INTERNAL ERROR"

Ή÷Ζϊ¥°ΒΡΉς”Ο÷ς“Σ”Ο”Ύ Ζ¬’φ Θ§œ‘ Ψ“Μ–©œύΙΊΒΡ–≈œΔΜρ’Ώ÷ΗΕ®œ‘ ΨΒΡΗώ ΫΓΘ

Θ®3Θ©≤Έ ΐ

Verilog÷–Θ§”Ο≤Έ ΐΘ®ΙΊΦϋΉ÷parameterΘ©ά¥Ε®“εΖϊΚ≈≥ΘΝΩΘ§Φ¥”Οparameterά¥Ε®“ε“ΜΗω±ξ÷ΨΖϊ¥ζ±μ“ΜΗω≥ΘΝΩΓΘΕ®“ε≤Έ ΐ≥Θ”Ο”ΎΕ®“ε ±―”ΚΆ±δΝΩΒΡΩμΕ»ΓΘ

”…”Ύ≤Μ‘ –μ÷ΗΕ®≤Έ ΐΒΡΈΜΩμΘ§“ρ¥ΥΤδΈΜΩμ”κΥυΕ‘”ΠΒΡ≥ΘΝΩΒΡΈΜΩμœύΆ§ΓΘœ¬ΟφΒΡ≤Έ ΐredΚΆgreen «ΝΫΗω32ΈΜΒΡΖϊΚ≈≥ΘΝΩΓΘREADYΓΔ

BUSY ΚΆEXIT «»ΐΗωΈΜΩμΈΣ2ΒΡ≤Έ ΐΓΘ

parameter red

= -1,

green = 2 ;

parameter READY = 2'b0 ;

patameter BUSY = 2'b11 ;

parameter EXIT = 2'b10 ; |

1.2. ÷Β±Θ≥÷ΤςΫ®ΡΘ

”≤Φΰ÷÷”–3÷÷Μυ±ΨΒΡ÷Β±Θ≥÷ΤςΘΚ

a) Ν§œΏ ΘΜ

b) ¥ΞΖΔΤς Θ®±Ώ―Ί¥ΞΖΔΒΡ¥φ¥ΔΤςΦΰΘ©ΘΜ

c) Υχ¥φΤςΘ®ΒγΤΫΟτΗ–ΒΡ¥φ¥ΔΤςΦΰΘ©

œ¬ΟφΫΪΫι…ήΙΊ”ΎΕ‘’β»ΐ÷÷ΤςΦΰΒΡΆΤΒΦΓΘ

‘Ύ«ΑΟφΈΜΩμ÷–Ϋι…ήΝΥΘ§Verilog÷–ΒΡ±δΝΩ ΐΨίάύ–ΆΦ»Ω…“‘ «ΆχœΏ–ΆΘ§“≤Ω…“‘ «ΦΡ¥φΤςάύ–ΆΓΘΉέΚœΒΡ ±ΚρΨΆΜαΑ―ΆχœΏάύ–Ά”≥…δ≥…”≤Φΰ÷–ΒΡΝ§œΏΘ§ΕχΦΡ¥φΤς±δΝΩ‘ρΜΙ–η“ΣΗυΨί±ΜΗ≥÷ΒΒΡ…œœ¬ΈΡΜΖΨ≥ά¥»ΖΕ®’βΗωΦΡ¥φΤς±δΝΩΒΫΒΉ «”≥…δ≥…Ν§œΏΜΙ «”≥…δ≥…¥φ¥ΔΤΎΦδΘ®¥ΞΖΔΤςΜρΥχ¥φΤςΘ©ΓΘ‘ΎVerilog

HDLΒΡ’ϊΗωΖ¬’φ‘Υ––Ιΐ≥Χ÷–Θ§ΦΡ¥φΤς±δΝΩ“Μ÷¬±Θ≥÷Ή‘ΦΚΒΡ÷ΒΘ§“ρΕχΑ―ΥϋΆΤΒΦ≥…¥φ¥ΔΤςΓΘΒΪ «ΉέΚœΒΡ ±Κρ≤Μ «ΨχΕ‘ΓΘ

ΓΨΉΔΓΩΘΚreg–Ά±δΝΩ≤Δ≤Μ“ΜΕ®ΕΦ «ΜαΉέΚœ≥…¥ΞΖΔΤςΜρΥχ¥φΤςΘ§“≤Ω…Ρή «”≤ΦΰΝ§œΏΓΘ

œ¬ΟφάΐΉ”÷–ΒΡ±δΝΩΫω”ΟΉς“ΜΗωΝΌ ±±δΝΩΘ§“ρΕχ ΟΜ”–±Ί“ΣΫΪΤδ”≥…δ≥…¥φ¥Δ‘ΣΦΰΓΘ

wire Acr,Bar

,Fra; //ΆχœΏ–Ά

reg Trq Θ§Sqb; //ΦΡ¥φΤς–Ά

...

always@(Bar or Acr or Fra)

begin

Trq = Bar & Acr ;

Sqb= Trq | Fra

end

|

…œΟφάΐΉ”÷–Θ§‘ΎalwaysΩι÷–Ε‘reg–Ά±δΝΩTrqΫχ––ΝΥΗ≥÷ΒΘ§»ΜΚσ‘Ύœ¬“ΜΨδ÷–Ε‘Sqb±δΝΩΗ≥÷Β±μ¥ο Ϋ÷–“ΐ”ΟΝΥΗΟ±δΝΩΓΘ¥”Verilgo

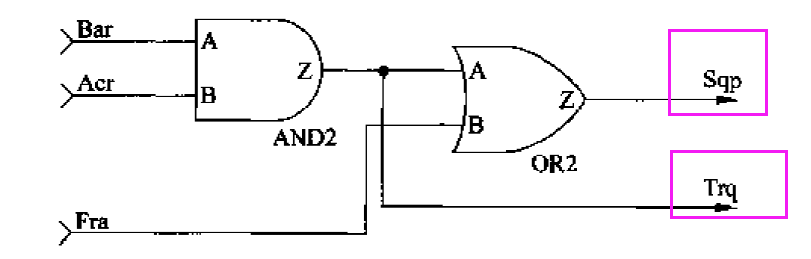

HDLΒΡ”ο“ε…œΩ¥Θ§‘Ύ’ϊΗωΖ¬’φΙΐ≥Χ÷–TrqΜα“Μ÷±±Θ≥÷ΥϋΒΡ÷ΒΓΘΒΪ «Θ§‘Ύ”≤Φΰ Βœ÷ ±Θ§ΟΜ”–±Ί“ΣΫΪTrqΒΡ÷Β±Θ≥÷‘Ύ”≤Φΰ¥φ¥Δ‘ΣΦΰ÷–Θ§“ρΈΣTrqΒΡ÷Β‘ΎΤδΗ≥÷ΒΆξ≥…÷°ΚσΨΆΝΔΦ¥±Μ“ΐ”ΟΝΥΓΘ“ρ¥ΥΘ§ΉέΚœΤςΉέΚœΚσ…ζ≥…ΒΡ¬ΏΦ≠Βγ¬Ζ»γΆΦ8Υυ ΨΘΚ

ΆΦ8ΘΚΉέΚœΚσΒΡTrq «ΒΦœΏ

œ÷ΦΌ»γΫΪalwaysΩι÷–ΝΫΗωΗ≥÷Β”οΨδΒςΜΜΥ≥–ρΘΚ

always@(Bar or

Acr or Fra)

begin

Sqb= Trq | Fra ;

Trq = Bar & Acr ;

end |

Υ≥–ρΒΡ±δΕ· ΙΒΟ±δΝΩTrq‘ΎΗ≥÷Β÷°«ΑΨΆ“Σ±Μ“ΐ”ΟΓΘalways”οΨδΩιΒΡ”ο“εΚήΟς»ΖΘ§÷Μ“Σ≥ωœ÷BarΓΔAcrΓΔFra

œύΙΊΒΡ ¬ΦΰΘ®Φ¥“ΜΒ©BarΓΔAcrΓΔFra”–±δΜ·Θ©Θ§ΨΆΜα÷¥––always”οΨδΓΘ“ρΈΣTrq‘Ύ±ΜΗ≥÷Β«ΑΨΆ‘Ύ±μ¥ο Ϋ÷–±Μ“ΐ”ΟΝΥΘ§“ρ¥Υ‘Ύ÷ΊΗ¥÷¥––always”οΨδΒΡΙΐ≥Χ÷–Trq≤ΜΒΟ≤Μ±Θ≥÷Τδ÷ΒΘ§“ρ¥ΥΜαΑ―ΥϋΆΤΒΦ≥…¥φ¥ΔΤςΘ®Θ©ΓΘ≤ΜΙΐΘ§’βΜΙ≤ΜΉψ“‘Ος»Ζ»γΚΈΑ―TrqΙΙ‘λ≥…Υχ¥φΤςΘ§“ρΈΣTrqΈ¥‘Ύ»ΈΚΈΧθΦΰΒΡΩΊ÷Τœ¬±ΜΗ≥÷ΒΓΘ¥Υ ±ΒΡΉέΚœΤςΩ…ΡήΈόΖ®ΈΣΤδΫ®ΝΔΥχ¥φΤςΘ§Εχ”–Ω…Ρή…ζ≥…ΆΦ9Υυ ΨΒΡΒγ¬ΖΓΘ±δΝΩTrq‘Ό¥ΈΜα±ΜΉέΚœ≥…ΆχœΏΓΘΒΪ «Θ§ΈΣ ΙΒΟVerilog

HDLΡΘ–Ά”κΉέΚœ≥ωΒΡΆχ±μΙΠΡή“Μ÷¬Θ§Trq“≤±Ί–κΖ≈»κalways”οΨδΒΡ ¬Φΰ±μ÷–ΓΘ

ΆΦ9ΘΚ±δΝΩTrq»‘»ΜΈ¥±ΜΉέΚœ≥…Υχ¥φΤς

ΫΪ±δΝΩTrqΆΤΒΦ≥…Υχ¥φΤςΒΡ ΨάΐΘΚ

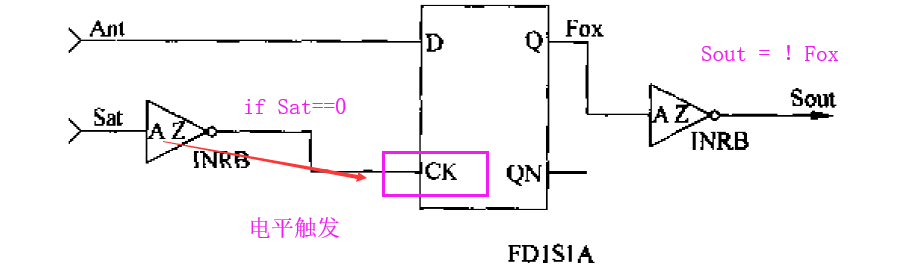

±δΝΩFox‘ΎΧθΦΰ”οΨδΒΡelseΖ÷÷ß÷–Έ¥±ΜΗ≥÷ΒΘ§÷Μ”–Β±SatΈΣΦΌ ±ΚρΈΣFoxΗ≥÷ΒΈΣAntȧѫϥ±SatΈΣ’φ ±Θ§ΨΆ–η“Σ±Θ¥φ±δΝΩFox÷–‘≠”–ΒΡ÷ΒΘ§’β ±ΚρΉέΚœΤςΨΆΜαΫΪFox±δΝΩΆΤΒΦ≥…Υχ¥φΤςΓΘΉΔ“βΘΚΟτΗ–Ν–±μ÷–Αϋά®ΝΥΧθΦΰΘΚΦ¥Sat¥ΞΖΔΒγΤΫΚΆ«ΐΕ·AntΓΘ

ΉέΚœ≥ωΒΡΒγ¬ΖΘΚ

ΆΦ10ΘΚ±δΝΩFoxΉέΚœ≥…Υχ¥φΤς

≤Ο¥―υΒΡHDL≤≈ΡήΆΤΒΦ≥ω¥ΞΖΔΤςΡΊΘΩ’β“≤»ΓΨω”Ύ≤…”Ο ΒΡΫ®ΡΘΖΫ ΫΚΆ±δΝΩ±ΜΗ≥÷ΒΒΡ…œœ¬ΈΡΜΖΨ≥ΓΘ‘ΎΘ®2Θ©¥”Verilog”οΨδΒΫ”≤Φΰ¬ΏΦ≠Ο≈ΒΡ”≥…δΘ§Ϋβ ΆΝΥ‘ΥΥψΖϊΓΔ±μ¥ο ΫΚΆΗ≥÷Β”οΨδ «»γΚΈ”≥…δ≥…”≤ΦΰΒΡ

ΜΙΜαΗυΨί’βΗωάΐΉ”“‘ΦΑΤδΥϊ ΨάΐΗϋœξœΗΒΊΫι…ή»γΚΈΆΤΒΦ≥ω¥ΞΖΔΤςΚΆΥχ¥φΤςΓΘ

|