| ±ύΦ≠ΆΤΦω: |

±ΨΈΡ÷ς“ΣΫι…ήΝΥ–ΨΤ§ICΒΡΖβΉΑ/≤β ‘Νς≥Χ

“‘ΦΑIC Package ΒΡΖ÷άύΖΫ ΫΘ§,œΘΆϊΕ‘ΡζΒΡ―ßœΑ”–ΥυΑο÷ζΓΘ

±ΨΈΡά¥Ή‘”ΎCSDNΘ§”…ΜπΝζΙϊ»μΦΰAlice±ύΦ≠ΓΔΆΤΦωΓΘ |

|

Νς≥Χ

IC Package (ICΒΡΖβΉΑ–Έ Ϋ)÷Η–ΨΤ§(Die)ΚΆ≤ΜΆ§άύ–ΆΒΡΩρΦή(L/F)ΚΆΥήΖβΝœ(EMC)–Έ≥…ΒΡ≤ΜΆ§Άβ–ΈΒΡΖβΉΑΧεΓΘ

IC Package÷÷άύΚήΕύΘ§Ω…“‘Α¥“‘œ¬±ξΉΦΖ÷άύΘΚ

Α¥ΖβΉΑ≤ΡΝœΜ°Ζ÷ΈΣΘΚ

Ϋπ τΖβΉΑΓΔΧ’¥…ΖβΉΑΓΔΥήΝœΖβΉΑ

Ϋπ τΖβΉΑ÷ς“Σ”Ο”ΎΨϋΙΛΜρΚΫΧλΦΦ θΘ§Έό…Χ“ΒΜ·≤ζΤΖ;

Χ’¥…ΖβΉΑ”≈”ΎΫπ τΖβΉΑΘ§“≤”Ο”ΎΨϋ ¬≤ζΤΖΘ§’Φ…ΌΝΩ…Χ“ΒΜ· –≥Γ;

ΥήΝœΖβΉΑ”Ο”ΎœϊΖ―ΒγΉ”Θ§“ρΈΣΤδ≥…±ΨΒΆΘ§ΙΛ“’ΦρΒΞΘ§Ω…ΩΩ–‘ΗΏΕχ’Φ”–Ψχ¥σ≤ΩΖ÷ΒΡ –≥ΓΖίΕν;

Α¥’’ΚΆPCBΑεΝ§Ϋ”ΖΫ ΫΖ÷ΈΣΘΚ

PTHΖβΉΑΚΆSMTΖβΉΑ

PTH-Pin Through Hole, Ά®ΩΉ Ϋ;

SMT-Surface Mount TechnologyΘ§±μΟφΧυΉΑ ΫΓΘ

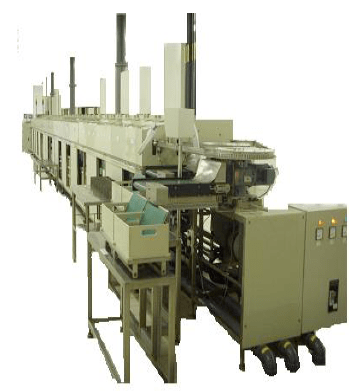

ΡΩ«Α –Οφ…œ¥σ≤ΩΖ÷ICΨυ≤…ΈΣSMT ΫΒΡ

Α¥’’ΖβΉΑΆβ–ΆΩ…Ζ÷ΈΣΘΚ

SOTΓΔSOICΓΔTSSOPΓΔQFNΓΔQFPΓΔBGAΓΔCSPΒ»;

ΨωΕ®ΖβΉΑ–Έ ΫΒΡΝΫΗωΙΊΦϋ“ρΥΊ:

ΖβΉΑ–߬ ΓΘ–ΨΤ§ΟφΜΐ/ΖβΉΑΟφΜΐΘ§ΨΓΝΩΫ”Ϋϋ1:1;

“ΐΫ≈ ΐΓΘ“ΐΫ≈ ΐ‘ΫΕύΘ§‘ΫΗΏΦΕΘ§ΒΪ «ΙΛ“’Ρ―Ε»“≤œύ”Π‘ωΦ”;

Τδ÷–Θ§CSP”…”Ύ≤…”ΟΝΥFlip ChipΦΦ θΚΆ¬ψΤ§ΖβΉΑΘ§¥οΒΫΝΥ –ΨΤ§ΟφΜΐ/ΖβΉΑΟφΜΐ=1:1Θ§ΈΣΡΩ«ΑΉνΗΏΦΕΒΡΦΦ θ;

QFNΓΣQuad Flat No-lead Package ΥΡΖΫΈό“ΐΫ≈±βΤΫΖβΉΑ

SOICΓΣSmall Outline IC –ΓΆβ–ΈICΖβΉΑ

TSSOPΓΣThin Small Shrink Outline Package ±Γ–ΓΆβ–ΈΖβΉΑ

QFPΓΣQuad Flat Package ΥΡΖΫ“ΐΫ≈±βΤΫ ΫΖβΉΑ

BGAΓΣBall Grid Array Package «ρ’Λ’σΝ– ΫΖβΉΑ

CSPΓΣChip Scale Package –ΨΤ§≥Ώ¥γΦΕΖβΉΑ

IC Package Structure(ICΫαΙΙΆΦ)

Raw Material in Assembly(ΖβΉΑ‘≠≤ΡΝœ)ΓΨWaferΓΩΨß‘≤

ΓΨLead FrameΓΩ“ΐœΏΩρΦή

ΧαΙ©Βγ¬ΖΝ§Ϋ”ΚΆDieΒΡΙΧΕ®Ής”Ο;

÷ς“Σ≤ΡΝœΈΣΆ≠Θ§Μα‘Ύ…œΟφΫχ––ΕΤ“χΓΔ NiPdAuΒ»≤ΡΝœ;

L/FΒΡ÷Τ≥Χ”–EtchΚΆStampΝΫ÷÷;

“Ή―θΜ·Θ§¥φΖ≈”ΎΒΣΤχΙώ÷–Θ§ ΣΕ»–Γ ”Ύ40%RH;

≥ΐΝΥBGAΚΆCSPΆβΘ§ΤδΥϊPackageΕΦΜα≤…”ΟLead FrameΘ§ BGA≤…”ΟΒΡ «Substrate;

ΓΨGold WireΓΩΚΗΫ”ΫπœΏ

Βœ÷–ΨΤ§ΚΆΆβ≤Ω“ΐœΏΩρΦήΒΡΒγ–‘ΚΆΈο άμΝ§Ϋ”;

ΫπœΏ≤…”ΟΒΡ «99.99%ΒΡΗΏ¥ΩΕ»Ϋπ;

Ά§ ±Θ§≥ω”Ύ≥…±ΨΩΦ¬«Θ§ΡΩ«Α”–≤…”ΟΆ≠ œΏΚΆ¬ΝœΏΙΛ“’ΒΡΓΘ”≈Βψ «≥…±ΨΫΒΒΆΘ§ Ά§ ±ΙΛ“’Ρ―Ε»Φ”¥σΘ§ΝΦ¬ ΫΒΒΆ;

œΏΨΕΨωΕ®Ω…¥ΪΒΦΒΡΒγΝς;0.8milΘ§ 1.0milΘ§1.3milsΘ§1.5milsΚΆ2.0mils;

Mold CompoundΥήΖβΝœ/ΜΖ―θ ς÷§÷ς“Σ≥…Ζ÷ΈΣΘΚΜΖ―θ ς÷§ΦΑΗς÷÷ΧμΦ”ΦΝ(ΙΧΜ·ΦΝΘ§ΗΡ–‘ΦΝΘ§Ά― ΡΘΦΝΘ§»Ψ…ΪΦΝΘ§Ήη»ΦΦΝΒ»);

÷ς“ΣΙΠΡήΈΣΘΚ‘Ύ»έ»ΎΉ¥Χ§œ¬ΫΪDieΚΆLead FrameΑϋΙϋΤπά¥Θ§ ΧαΙ©ΈοάμΚΆΒγΤχ±ΘΜΛΘ§Ζά÷ΙΆβΫγΗ…»≈;

¥φΖ≈ΧθΦΰΘΚΝψœ¬5Γψ±Θ¥φΘ§≥ΘΈ¬œ¬–ηΜΊΈ¬24–Γ ±;

ΓΨEpoxyΓΩ“χΫ§

≥…Ζ÷ΈΣΜΖ―θ ς÷§Χν≥δΫπ τΖέΡ©(Ag);”–»ΐΗωΉς”ΟΘΚΫΪDieΙΧΕ®‘ΎDie Pad…œ; …Δ»»Ής”ΟΘ§ΒΦΒγΉς”Ο;

-50Γψ“‘œ¬¥φΖ≈Θ§ Ι”Ο÷°«ΑΜΊΈ¬24–Γ ±;

FOL®C Front of Line«ΑΕΈΙΛ“’

FOL®C Back Grinding±≥ΟφΦθ±Γ

ΫΪ¥”Ψß‘≤≥ß≥ωά¥ΒΡWaferΫχ––±≥Οφ―–ΡΞΘ§ά¥Φθ±ΓΨß‘≤¥οΒΫ ΖβΉΑ–η“ΣΒΡΚώΕ»(8mils~10mils);

ΡΞΤ§ ±Θ§–η“Σ‘Ύ’ΐΟφ(Active Area)ΧυΫΚ¥χ±ΘΜΛΒγ¬Ζ«χ”ρ Ά§ ±―–ΡΞ±≥ΟφΓΘ―–ΡΞ÷°ΚσΘ§»Ξ≥ΐΫΚ¥χΘ§≤βΝΩΚώΕ»;

FOL®C Wafer SawΨß‘≤«–Ην

ΫΪΨß‘≤’≥Χυ‘ΎάΕΡΛ(Mylar)…œΘ§ ΙΒΟΦ¥ Ι±Μ«–ΗνΩΣΚσΘ§≤ΜΜα…Δ¬δ;

Ά®ΙΐSaw BladeΫΪ’ϊΤ§Wafer«–Ην≥…“ΜΗωΗωΕάΝΔΒΡDiceΘ§ΖΫ±ψΚσΟφΒΡ Die AttachΒ»ΙΛ–ρ;

Wafer Wash÷ς“Σ«εœ¥Saw ±Κρ≤ζ…ζΒΡΗς÷÷Ζέ≥ΨΘ§«εΫύWafer;

FOL®C 2nd Optical InspectionΕΰΙβΦλ≤ι

÷ς“Σ «’κΕ‘Wafer Saw÷°Κσ‘Ύœ‘ΈΔΨΒœ¬Ϋχ––WaferΒΡΆβΙέΦλ≤ιΘ§ «Ζώ”–≥ωœ÷ΖœΤΖΓΘ

FOL®C Die Attach –ΨΤ§’≥Ϋ”

–ΨΤ§ Α»ΓΙΐ≥ΧΘΚ

1ΓΔEjector Pin¥”waferœ¬ΖΫΒΡMylarΕΞΤπ–ΨΤ§Θ§ Ι÷°±ψ”Ύ Ά―άκάΕΡΛ;

2ΓΔCollect/Pick up head¥”…œΖΫΈϋΤπ–ΨΤ§Θ§Άξ≥…¥”Wafer ΒΫL/FΒΡ‘Υ δΙΐ≥Χ;

3ΓΔCollect“‘“ΜΕ®ΒΡΝΠΫΪ–ΨΤ§Bond‘ΎΒψ”–“χΫ§ΒΡL/F ΒΡPad…œΘ§ΨΏΧεΈΜ÷ΟΩ…ΩΊ;

4ΓΔBond Head ResolutionΘΚX-0.2um;Y-0.5um;Z-1.25um;

5ΓΔBond Head SpeedΘΚ1.3m/s;

FOL®C Epoxy Cure “χΫ§ΙΧΜ·

“χΫ§ΙΧΜ·ΘΚ

175ΓψCΘ§1Ηω–Γ ±; N2ΜΖΨ≥Θ§Ζά÷Ι―θΜ·ΘΚ

Die Attach÷ ΝΩΦλ≤ιΘΚ

Die Shear(–ΨΤ§Φτ«–ΝΠ)

FOL®C Wire Bonding “ΐœΏΚΗΫ”

άϊ”ΟΗΏ¥ΩΕ»ΒΡΫπœΏ(Au) ΓΔΆ≠œΏ(Cu)Μρ¬ΝœΏ(Al)Α― Pad ΚΆ LeadΆ®ΙΐΚΗΫ”ΒΡΖΫΖ®Ν§Ϋ”Τπά¥ΓΘPad «–ΨΤ§…œΒγ¬ΖΒΡΆβΫ”

ΒψΘ§Lead « Lead Frame…œΒΡ Ν§Ϋ”ΒψΓΘ

W/B «ΖβΉΑΙΛ“’÷–ΉνΈΣΙΊΦϋΒΡ“Μ≤ΩΙΛ“’ΓΘ

FOL®C 3rd Optical Inspection»ΐΙβΦλ≤ι

EOL®C End of LineΚσΕΈΙΛ“’

EOL®C Molding(ΉΔΥή)

EOL®C Laser Mark(ΦΛΙβ¥ρΉ÷)

‘Ύ≤ζΤΖ(Package)ΒΡ’ΐΟφΜρ’Ώ±≥ΟφΦΛΙβΩΧΉ÷ΓΘΡΎ»ί”–ΘΚ≤ζΤΖΟϊ≥ΤΘ§…ζ≤ζ»’ΤΎΘ§…ζ≤ζ≈ζ¥ΈΒ»;

EOL®C Post Mold Cure(ΡΘΚσΙΧΜ·)

”Ο”ΎMoldingΚσΥήΖβΝœΒΡΙΧΜ·Θ§±ΘΜΛICΡΎ≤ΩΫαΙΙΘ§œϊ≥ΐΡΎ≤Ω”ΠΝΠΓΘCure TempΘΚ175+/-5ΓψC;Cure

TimeΘΚ8Hrs

EOL®C De-flash(»Ξ“γΝœ)

ΡΩΒΡΘΚDe-flashΒΡΡΩΒΡ‘Ύ”Ύ»Ξ≥ΐMoldingΚσ‘ΎΙήΧε÷ήΈßLead÷°Φδ Εύ”ύΒΡ“γΝœ; ΖΫΖ®ΘΚ»θΥαΫΰ≈ίΘ§ΗΏ―ΙΥ°≥εœ¥;

EOL®C Plating(ΒγΕΤ)

άϊ”ΟΫπ τΚΆΜ·―ßΒΡΖΫΖ®Θ§‘ΎLeadframeΒΡ±μΟφ ΕΤ…œ“Μ≤ψΕΤ≤ψΘ§“‘Ζά÷ΙΆβΫγΜΖΨ≥ΒΡ”Αœλ(≥± Σ ΚΆ»»)ΓΘ≤Δ«“ Ι‘ΣΤςΦΰ‘ΎPCBΑε…œ»ί“ΉΚΗΫ”ΦΑ

ΧαΗΏΒΦΒγ–‘ΓΘ

ΒγΕΤ“ΜΑψ”–ΝΫ÷÷άύ–ΆΘΚ

Pb-FreeΘΚΈό«ΠΒγΕΤΘ§≤…”ΟΒΡ «>99.95%ΒΡΗΏ¥Ω Ε»ΒΡΈΐ(Tin)Θ§ΈΣΡΩ«ΑΤ’±ι≤…”ΟΒΡΦΦ θΘ§ΖϊΚœ

RoHSΒΡ“Σ«σ;

Tin-LeadΘΚ«ΠΈΐΚœΫπΓΘTin’Φ85%Θ§Lead’Φ 15%Θ§”…”Ύ≤ΜΖϊΚœ RoHSΘ§ΡΩ«ΑΜυ±Ψ±ΜΧ‘Χ≠;

EOL®C Post Annealing Bake(ΒγΕΤΆΥΜπ)

ΡΩΒΡΘΚ»ΟΈό«ΠΒγΕΤΚσΒΡ≤ζΤΖ‘ΎΗΏΈ¬œ¬ΚφΩΨ“ΜΕΈ ±ΦδΘ§ΡΩΒΡ‘Ύ”Ύ œϊ≥ΐΒγΕΤ≤ψ«±‘ΎΒΡΨß–κ…ζ≥Λ(Whisker

Growth)ΒΡΈ Χβ; ΧθΦΰΘΚ150+/-5C; 2Hrs;

EOL®C Trim&Form(«–Ϋν≥…–Ά)

TrimΘΚΫΪ“ΜΧθΤ§ΒΡLead Frame«–Ην≥…ΒΞΕάΒΡUnit(IC)ΒΡΙΐ≥Χ; FormΘΚΕ‘TrimΚσΒΡIC≤ζΤΖΫχ––“ΐΫ≈≥…–ΆΘ§¥οΒΫΙΛ“’–η“Σ«σΒΡ–ΈΉ¥Θ§

≤ΔΖ≈÷ΟΫχTubeΜρ’ΏTray≈Χ÷–;

EOL®C Final Visual Inspection(ΒΎΥΡΒάΙβΦλ)

‘ΎΒΆ±ΕΖ≈¥σΨΒœ¬Θ§Ε‘≤ζΤΖΆβΙέΫχ––Φλ≤ιΓΘ÷ς“Σ’κΕ‘EOLΙΛ“’Ω…Ρή≤ζ…ζΒΡΖœΤΖΘΚάΐ»γMolding»±œίΘ§ΒγΕΤ»±œίΚΆTrim/Form»±œίΒ»;

|