| 编辑推荐: |

本文主要介绍了嵌入式内核架构原理,及当前嵌入式市场主流MCU内核架构。 希望对你的学习有帮助。

本文来自于微信公众号阿宝1990,由火龙果软件Linda编辑、推荐。 |

|

本文主要介绍嵌入式内核架构原理,及当前嵌入式市场主流MCU内核架构。

#01 前 言

1.1 内核简介

计算机芯片内核架构(Processor Core Architecture)是指构成微处理器芯片的基本设计和组织结构,它定义了处理器执行指令、处理数据和控制程序执行的方式。简单来说,如果把大脑比作CPU,内核架构就相当于大脑内部各种中枢的组成和工作原理。不同系列的芯片根据使用场景和需求,采用不同的内核架构。

计算机内核离不开内核指令集,内核指令集是计算机内核编程接口的具体形式,它将计算机内核的操作通过整合和拆分,最终组织成一套能够实现内核控制的指令系统。

不同的内核具有不同的内核指令集,比如我们日常使用的计算机(Intel或AMD芯片),使用的就是X86指令集,内核就属于X86架构。常见的还有ARM架构、DSP架构和RISC-V架构。当我们想要掌握某款芯片,基于该芯片进行系统搭建时,就必须要了解该芯片的内核。

内核与指令集之间的关系是密切且复杂的,每种内核架构都有与之匹配的内核指令集,而内核与指令集之间有对应的版本匹配关系,例如,Cortex-A8和Cortex-A9内核是基于ARMv7-A指令集架构的,而Cortex-M3和Cortex-M4则是基于ARMv7-M指令集架构的。这里的"v7-A"和"v7-M"就是指令集架构的版本,代表它们支持的指令集类型。

1.2 内核分类

计算机内核指令集按照指令类型可以分为两种,一种是精简指令集(RISC,Reduced Instruction

Set Computing)计算机,它是一种计算机处理器架构设计理念,其核心思想是将处理器的指令集设计得相对较小和简单,以提高执行效率。RISC架构强调用更少、更基本的指令来完成操作,并且这些指令的执行时间相对较短。

另外一种是复杂指令集(CISC)计算机,是一种计算机处理器设计模式,其主要特征是支持大量的、复杂的指令系统。CISC架构的设计理念是通过设置一些功能复杂的指令,把一些原来由软件实现的、常用的功能改用硬件指令实现,以此来提高计算机的执行速度。这种设计使得CISC架构的处理器拥有大量且种类繁多的指令,包括基础算术逻辑运算、数据传输、控制转移、处理器状态管理、高级数据处理以及系统级指令等。

内核的分类一般是与指令集相匹配的,毕竟是共生设计出来的,比如与精简指令集配套的就是精简指令集内核架构。

嵌入式领域的芯片一般都是精简指令集内核架构,这符合嵌入式领域资源需求低,实时性要求高等特点。

#02 内核介绍

从计算机原理的角度来说,内核架构主要包括内核的运算方式、指令系统、CPU的结构和功能、中断系统等。

2.1 内核数据类型及运算方式

每一种内核,都有其固定的参与运算的各种数据类型,以及它们在内核中的算术运算方法。

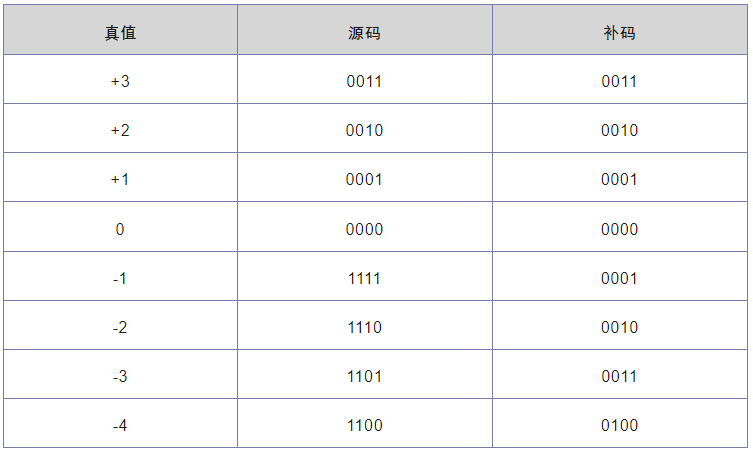

对于数据类型来说,内核的数据类型有两种:有符号和无符号。其按照原码、补码、反码的形式在内存中做具体实现。

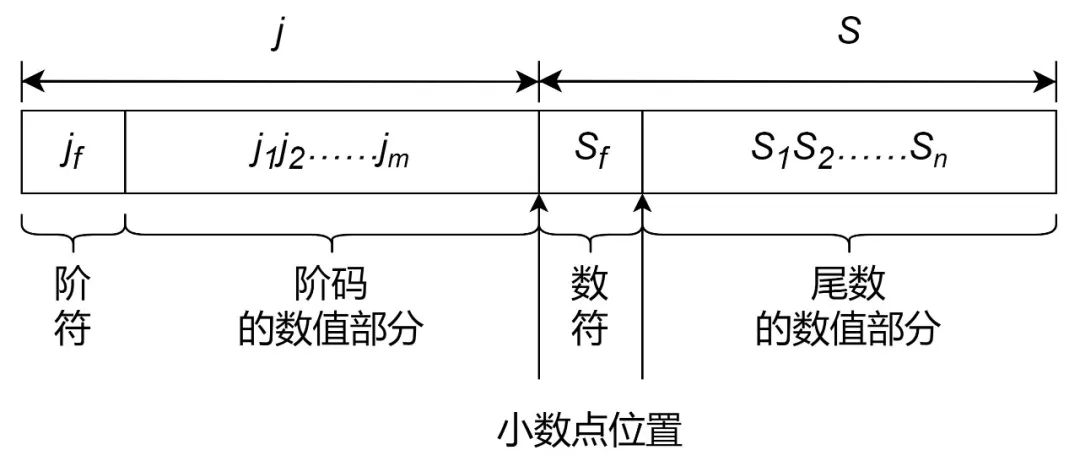

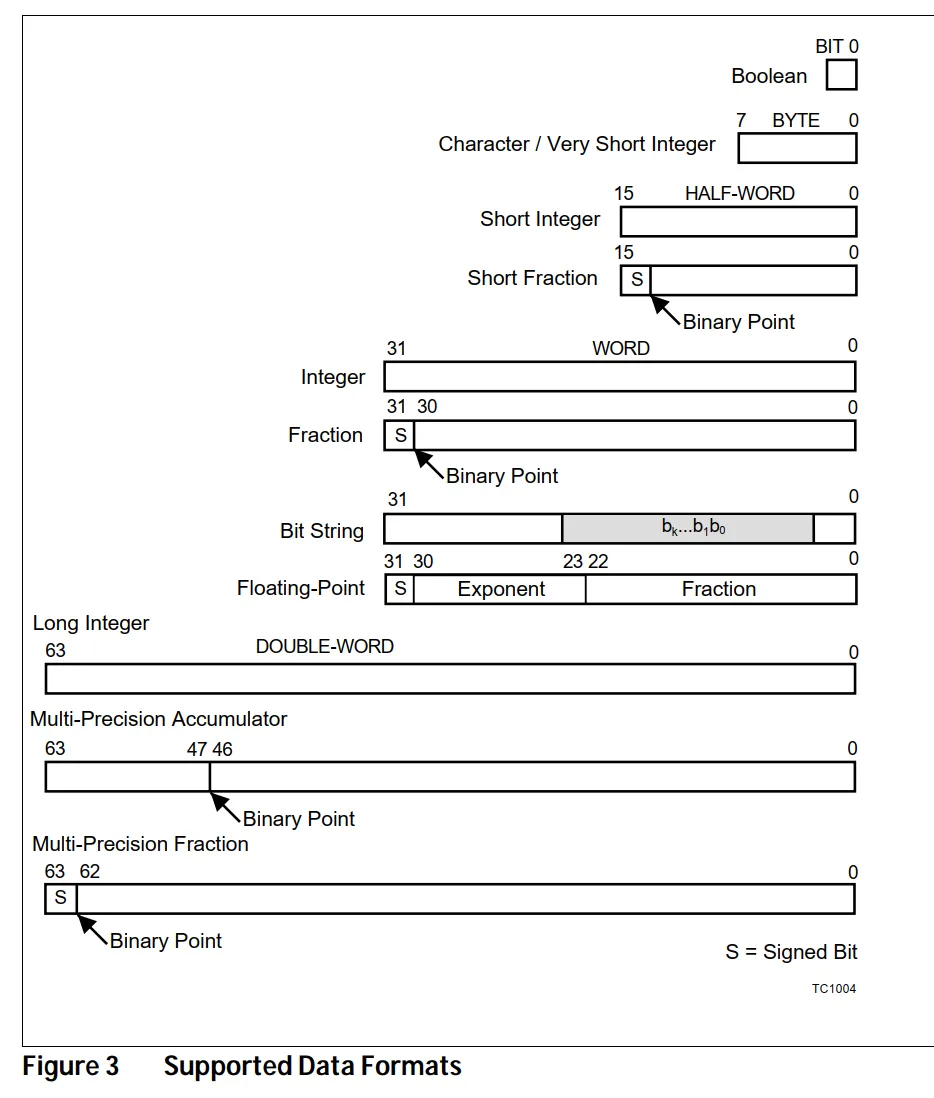

对于小数的表示,分为定点数和浮点数。定点数即小数点在固定的位置,浮点数则使用科学计数法,将数值分为4个部分,嵌入式内核一般使用浮点数表示法。

一般来说,这些数据类型在各类嵌入式系统中都是支持的,并没有太大的差异。下图是英飞凌TriCore

1.6.2架构中所支持的数据类型。

而在运算方式上,RISC架构下主要包括加减乘除、移位等运算,不同的内核硬件处理方式速度上表现略有不同。

2.2 指令系统

我们知道,在编写嵌入式代码时,我们使用的C语言属于高级语言;然后需要使用编译器将其编译成机器语言,也就是汇编语言;最终烧录到机器中,内核将其译码,然后真正地执行。

对于普通程序员来说,只需要学习C语言、C++等高级语言,一般不需要关心下层细节,因为编译器会做隔离。

对于不同类型地内核架构,因其内部硬件机制的不同,产生了不同的机器语言,而面向用户则需要提供配套的机器语言。人们习惯把每一条机器语言的语句称为机器指令,而又将全部机器指令的集合称为机器的指令系统。

不同的内核有着截然不同的指令系统,即使同系列的如ArmV7-M与ArmV7-A之间也有些许差异。

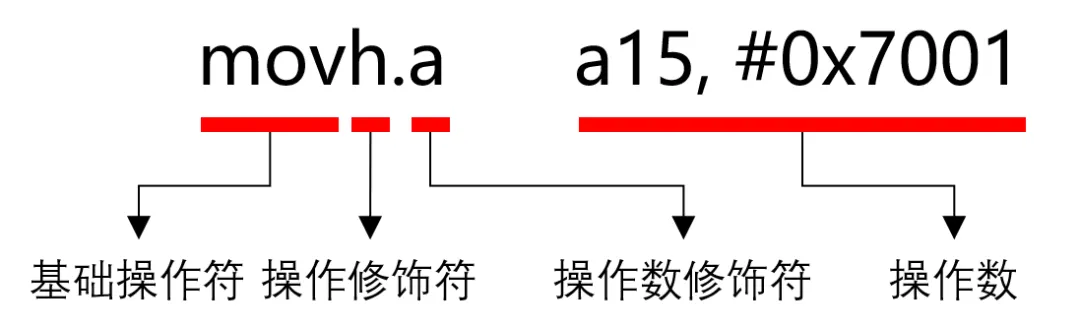

指令格式

指令的一般有两部分组成,操作码和地址码。

操作码用来指明该指令所要完成的操作,如加法、减法、传送、移位等。其位数反映了内核所能支持的操作类型数量,比如操作码占7位,则该内核最多包含2^7=128种指令。

地址码用来指出该指令的源操作数的地址、结果的地址以及下一条指令的地址。这里的地址可以是内存的地址,也可以是寄存器的地址、栈的地址。

不同的内核机器指令字长不同,嵌入式MCU的指令字长一般是32位,大多数内核也同时支持16位指令,用以精简代码容量。

操作数

一条完整的汇编代码一般包含指令和操作数,操作数的常见类型有地址、数字、字符、逻辑数等。

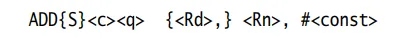

下面是ArmV7-M中一条加法指令的格式,包括一条加法指令两个寄存器和一个立即数:

寻址方式

寻址方式是指确定本条指令的数据地址以及下一条将要执行的指令地址的方法,它与硬件结构紧密相关,而且直接指令格式和指令功能。寻址方式主要分为指令寻址和数据寻址两种。

指令寻址比较简单,有我们常见的程序执行完之后PC自动累加,执行下一条指令,称为顺序寻址;还有一些跳转类的指令,如Jump等称为跳跃寻址。

数据寻址的方式就比较丰富了,它包括立即寻址、直接寻址、隐含寻址、间接寻址、寄存器寻址、寄存器间接寻址、基址寻址、变址寻址、相对寻址、堆栈寻址等模式。

如下图中列出英飞凌TriCore的加法指令的几种形式,有立即寻址、寄存器寻址、隐含寻址等方式。

另外除了这些常规的数据操作指令,根据不同内核的机制和特性,还存在一些具有内核特色的特殊指令,比如ARM中的数据屏障指令DSB,TriCore的低上下文保存指令SVLCX。

RISC VS CISC

RISC指令系统相对于CISC指令系统,因为采用了更少的指令,因此内核的芯片电路设计上要节省更多的面积,这些面积能够供其他功能使用,如提供更多的寄存器。

另外由于指令种类少、通用寄存器多、流水线设计友好等特性,RISC一般运算速度要高于CISC。

2.3 CPU结构与功能

CPU结构

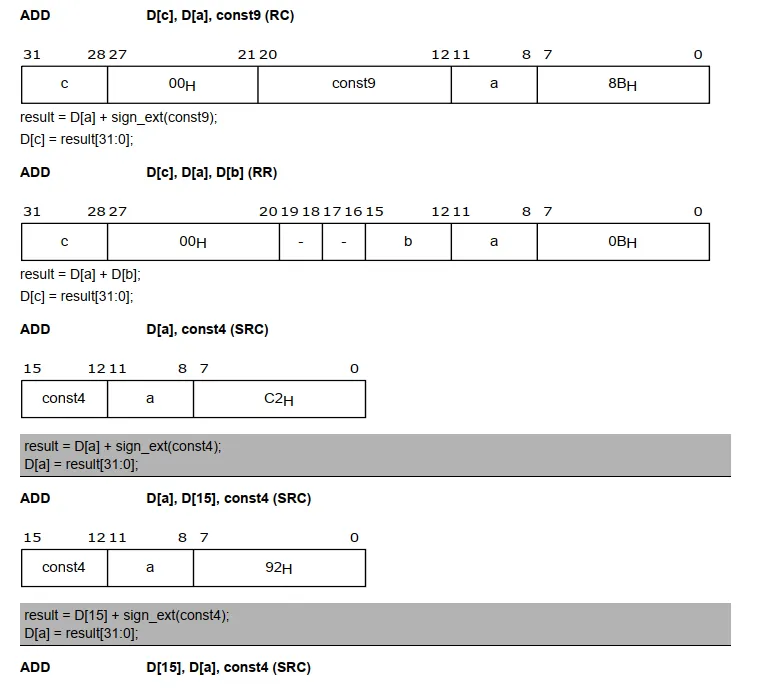

CPU实质包含运算器和控制器两大部分。如下图所示,一般计算机内核的最小系统中包括逻辑运算单元ALU、寄存器、中断系统、控制部件CU。

寄存器

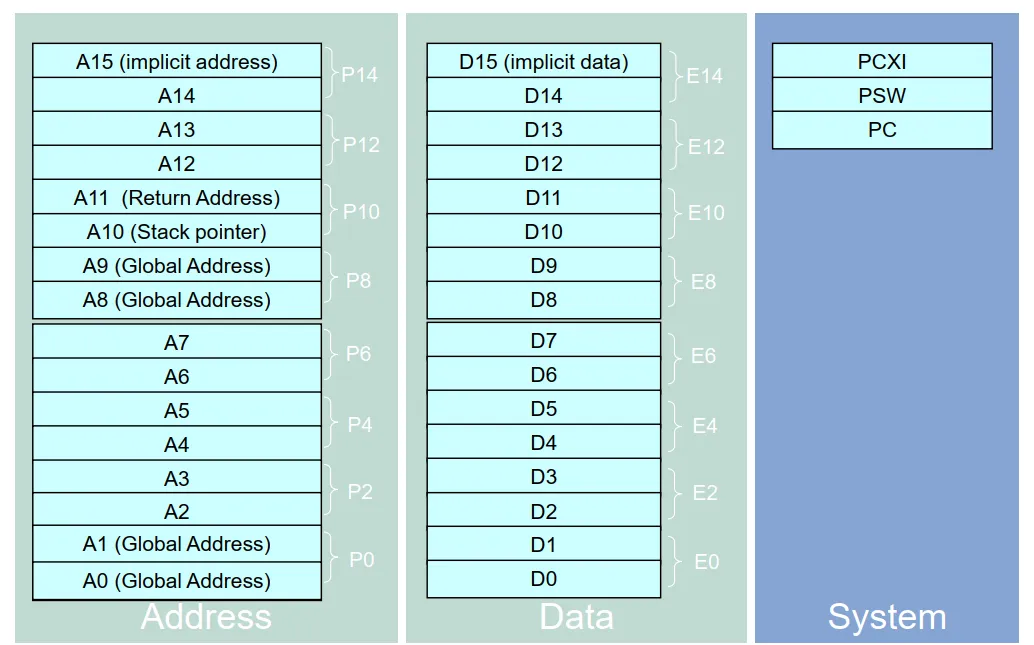

寄存器是计算机芯片中速度最快、容量最小、位价最贵的内存,它们设在CPU内部,用于CPU各种控制和运算。寄存器大致可分为两类:一类属于普通用户寄存器,用于常规计算使用,包括通用寄存器、数据寄存器、地址寄存器等;另一类是控制和状态寄存器,用于控制CPU的状态等,一般由操作系统等特权程序使用。

一般我们说某款芯片是多少位,如32位等,是说这款芯片的数据处理宽度,通常也是寄存器宽度。嵌入式领域中的芯片寄存器宽度一般是32位。

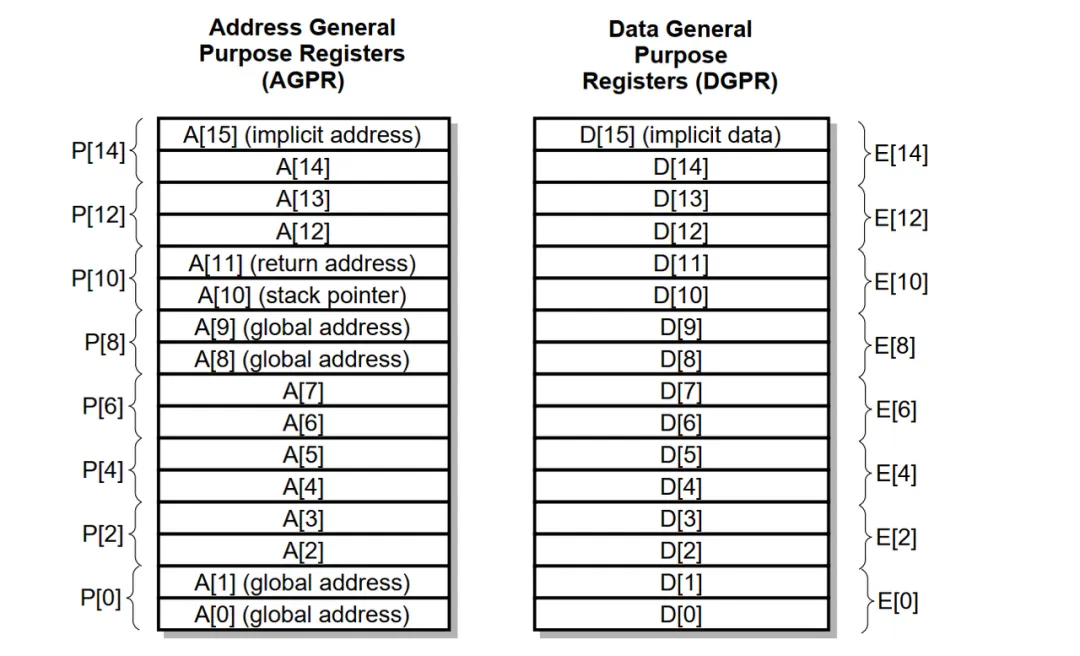

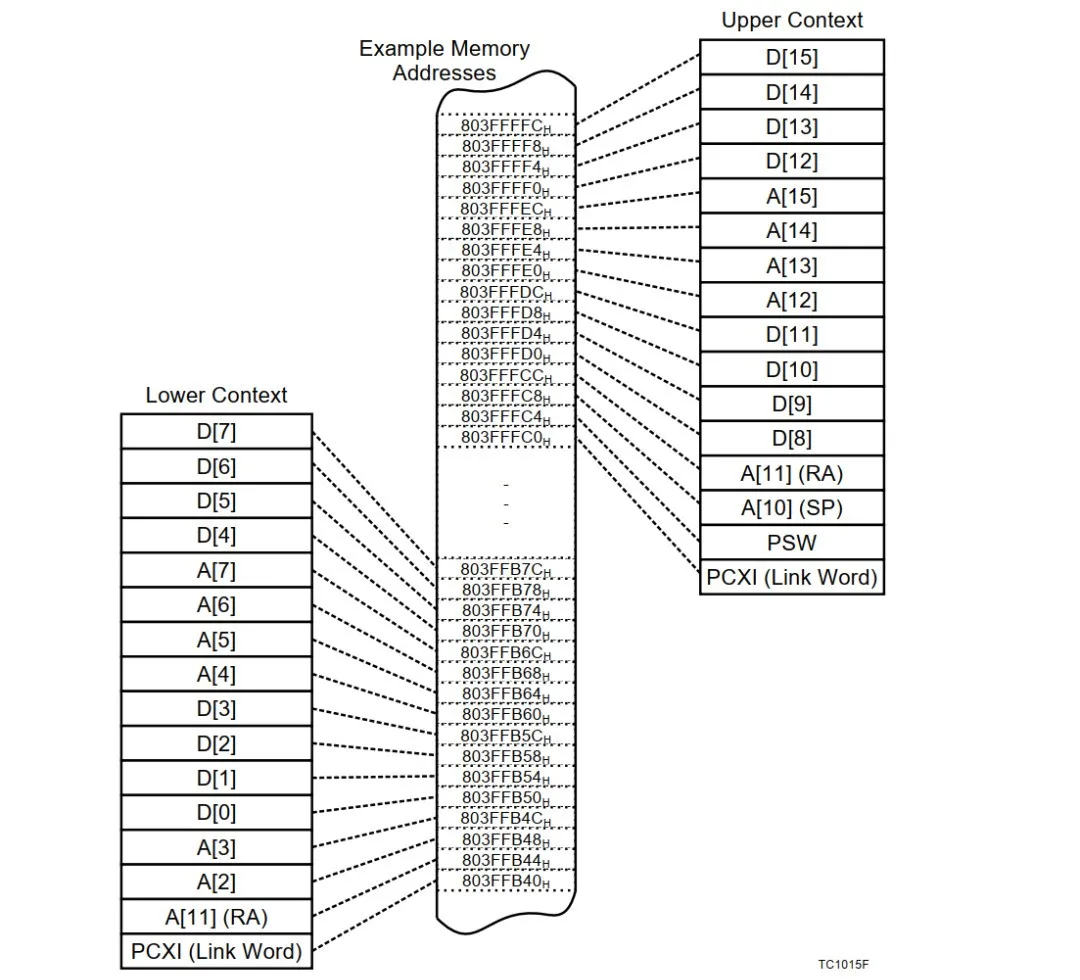

不同的内核,根据其结构设计不同,有不同的寄存器结构。比如下图中英飞凌的TriCore内核寄存器,除了常规的16个数据寄存器以外,还增加了16个地址寄存器,其中包括栈指针寄存器和返回地址寄存器,系统寄存器中则有专用其上下文系统使用的PCXI寄存器。

指令周期和指令流水

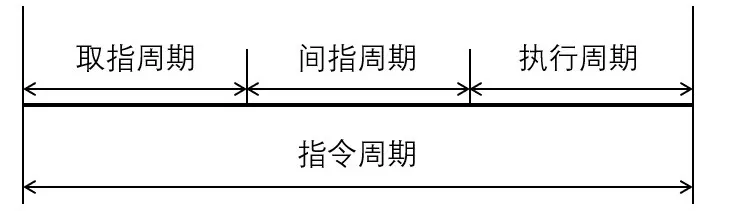

CPU取出一条指令并执行所需的全部时间称为指令周期。一般情况下,一个指令周期包含多个操作流程,比如当遇到间接寻址的指令时,需要经过以此间接寻址,因此指令执行分为三部分。

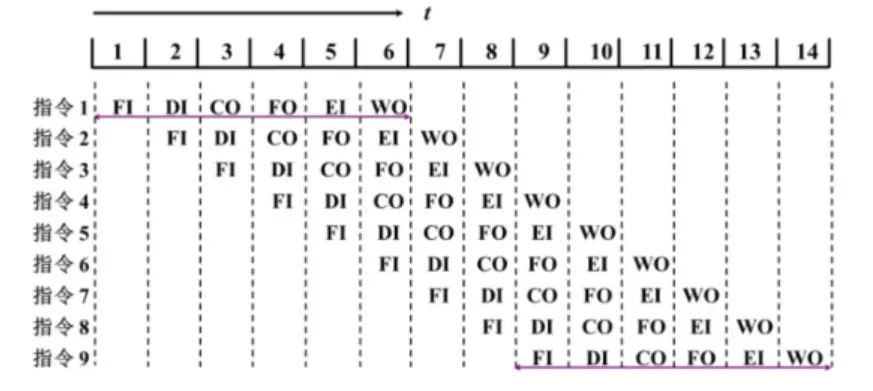

CPU中机器指令的每个操作流程一般对应一个硬件单元,称为指令部件,这些硬件单元在程序中接力完成指令执行,就像是流水线一样。假设我们将指令的流程分为6步:取值(FI)、指令译码(DI)、计算操作数地址(CO)、取操作数(FO)、执行指令(EI)、写操作数(WO),如下图中,当时间进行到第2列时,指令1已经完成了FI进入到DI,此时FI指令部件能够对下一条指令进行取值,实现并行,而在同一时刻,最多有6条指令在同时处理(下图同一列),这种技术称为指令流水,而根据流水部件数量,图中的流水称为六级流水。

当然,程序的执行有前后依赖的,指令流水能做到多流畅,除了取决于芯片厂商的流水线设计能力,还取决于代码逻辑。通常影响流水的因素有结构相关、数据相关、控制相关等。

流水线多发

一定程度来说,流水线技术从空间上加速了程序的执行。而为了进一步发展,还可以进行流水线多发技术,在一个时钟周期内产生更多条指令的结果,简单来说,就是增设多条流水线。最常见的就是超标量技术、超流水线技术、超长指令字技术。

下图中展示的就是多条流水并行的超标量技术,可以看到有四级三条流水并发,最多12条指令同时执行。但是同样受限于程序执行逻辑及顺序,其对编译优化的依赖较强。

2.4 中断系统

不管是嵌入式领域,还是其他计算机,程序在运行过程中要与外界通过I/O进行交互,因此会接收到外界的各种信号,以及定时器事件、程序异常等特殊事件。对于这些特殊事件需要进行及时响应,也就是暂停当前的程序立即前往指定的代码处处理对应的逻辑,该流程称为中断。广义的中断包括中断和异常。

因此对于各种内核架构,都需要设计出中断系统,以应对各种需要的中断场景。

中断因素

引起中断的因素有很多,如人为设置的软件中断,数据溢出、空指针等异常类中断,还有硬件故障类中断。另外当我们设置完硬件之后,硬件一旦完成操作或者就绪,就会发出中断如ADC中断、SPI中断等。

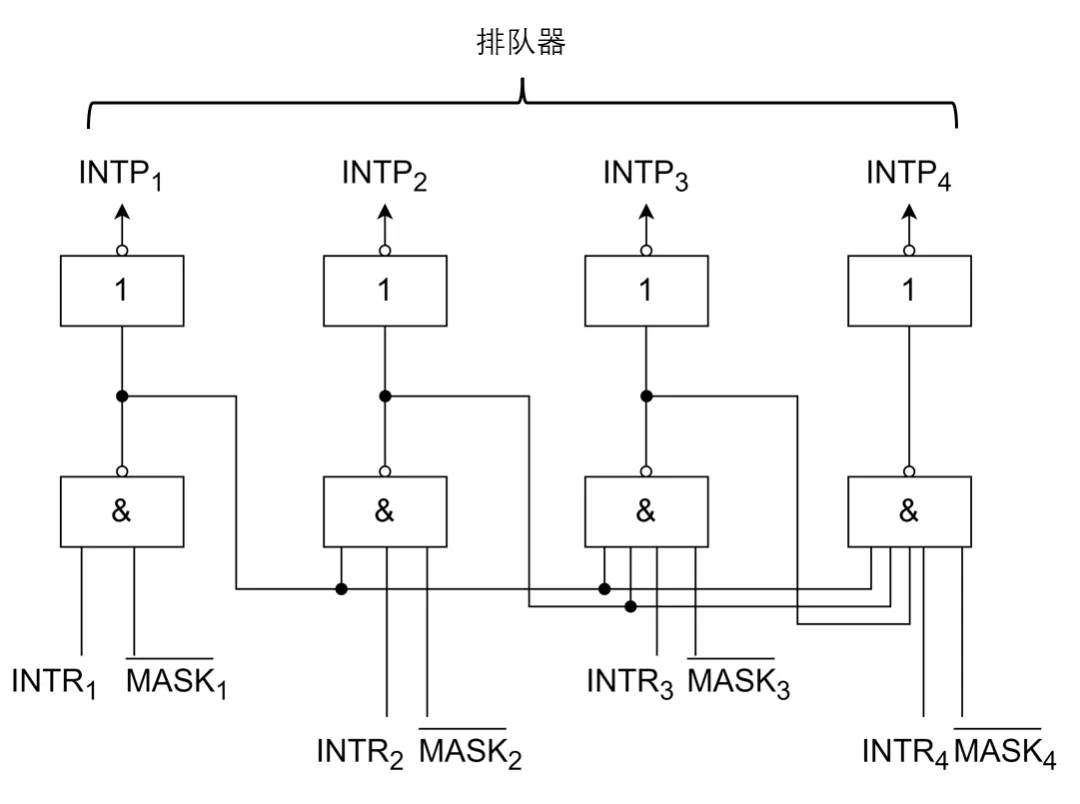

中断响应

在内核执行每一条指令之后,会去查询中断状态,判断是否有中断产生,这也是中断响应的最小时间颗粒度。当多个中断同时产生时,在嵌入式MCU领域,一般需要根据优先级进行排序。并且当高优先级中断执行时,低优先级中断不能够进行打断,下图是带有屏蔽和排队功能的中断系统逻辑电路示意图。

中断处理

中断处理流程一般包括保护现场、处理中断服务程序、恢复现场等流程。对于不同内核有着不同的处理机制,有的厂商还会再为了提供实时性做一些特殊设计,比如TriCore的自动上下文保存机制。

#03 主流嵌入式内核

3.1 内核市场现状

嵌入式常见的内核架构有ARM公司设计的ARM(Advanced RISC Machine)架构,SiFive公司的RISC-V(Reduced

Instruction Set Computer - Fifth Generation)架构,瑞萨公司的G4MH架构,英飞凌的TriCore架构等。

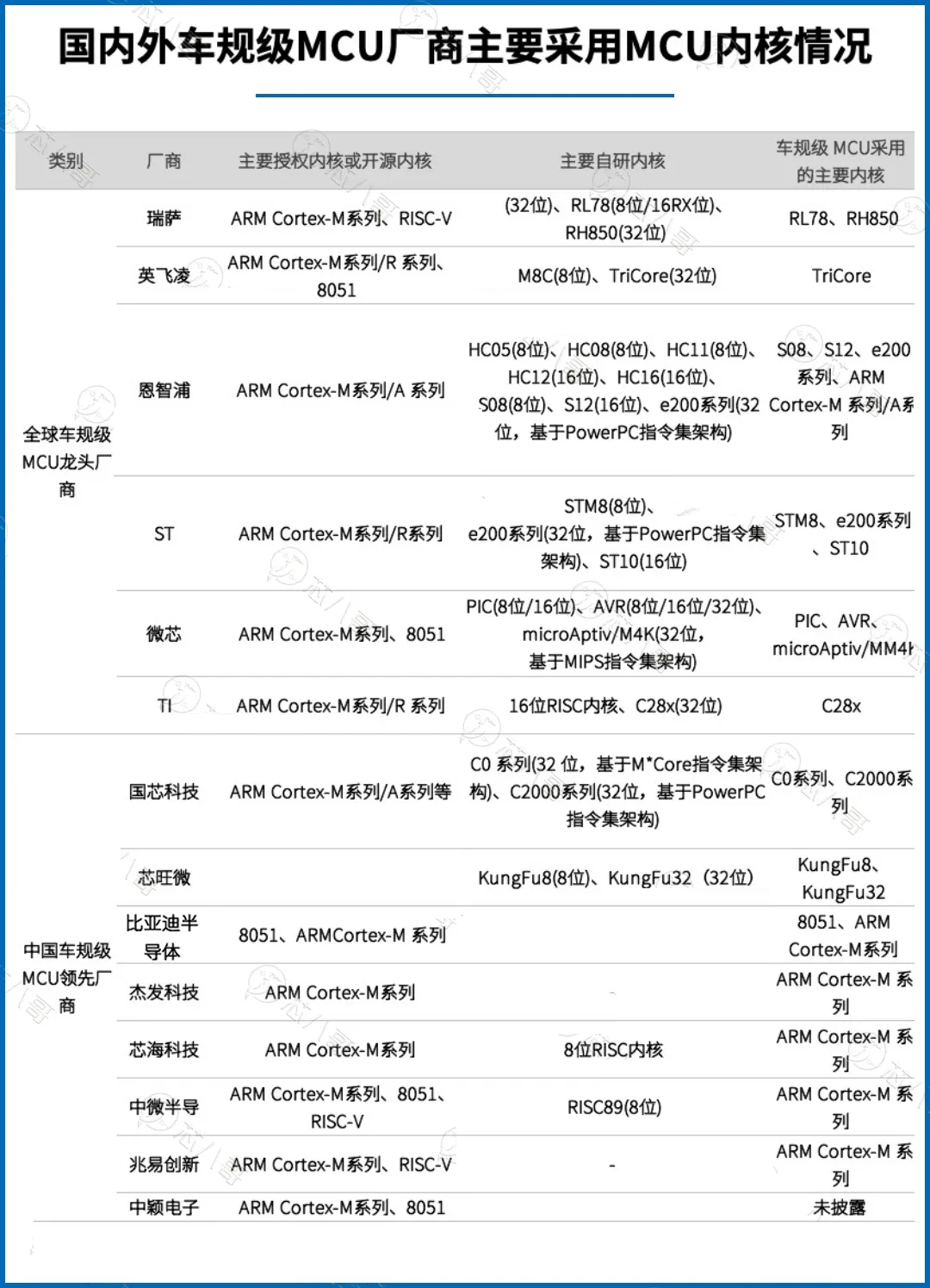

芯片厂商进行芯片研发的模式基本上有三种,一种是购买内核授权进行芯片设计开发,如购买ARM,Synopsys;一种是厂商自行研发内核;还有一种就是开源内核,如RISC-V。下图列出了当前国内外主流厂商MCU内核使用情况。

资料来源:各公司财报/官网、芯八哥整理

从图中可以看出,在授权领域各大厂商还是普遍采购ARM内核,来进行自家的芯片研发,嵌入式领域使用比较广泛的还是ARM

Cortex-M系列。而在开源领域RISC-V几乎是大家的不二之选,经历了十几年的发展也逐渐趋于稳定。而在自研内核领域里,比较广为人知的要数英飞凌的TriCore架构以及瑞萨的G4MH架构。

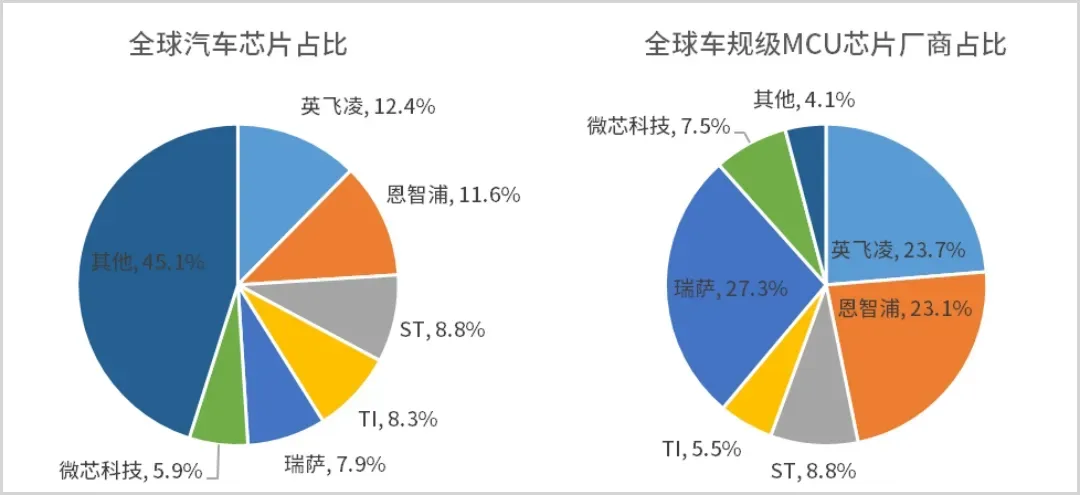

根据统计显示,车规MCU市场前三家瑞萨、恩智浦、英飞凌占据了余约70%多的份额。

资料来源:各公司财报/官网、芯八哥整理

下面我们介绍以下市场上三类主流的内核架构。

3.2 ARM Cortex-M内核

ARM的历史可以追溯到1978年,当时Acorn Computers由Chris Curry和Hermann

Hauser共同创立。1993年,搭载ARM的诺基亚6110 GSM手机取得了巨大成功,使得ARM7处理器成为ARM的旗舰移动设计,当今全球超过99%的智能手机都基于ARM技术。

随着公司的发展,ARM的产品线也日益多样化,2000年代推出了Cortex-A、Cortex-R和Cortex-M

CPU处理器。

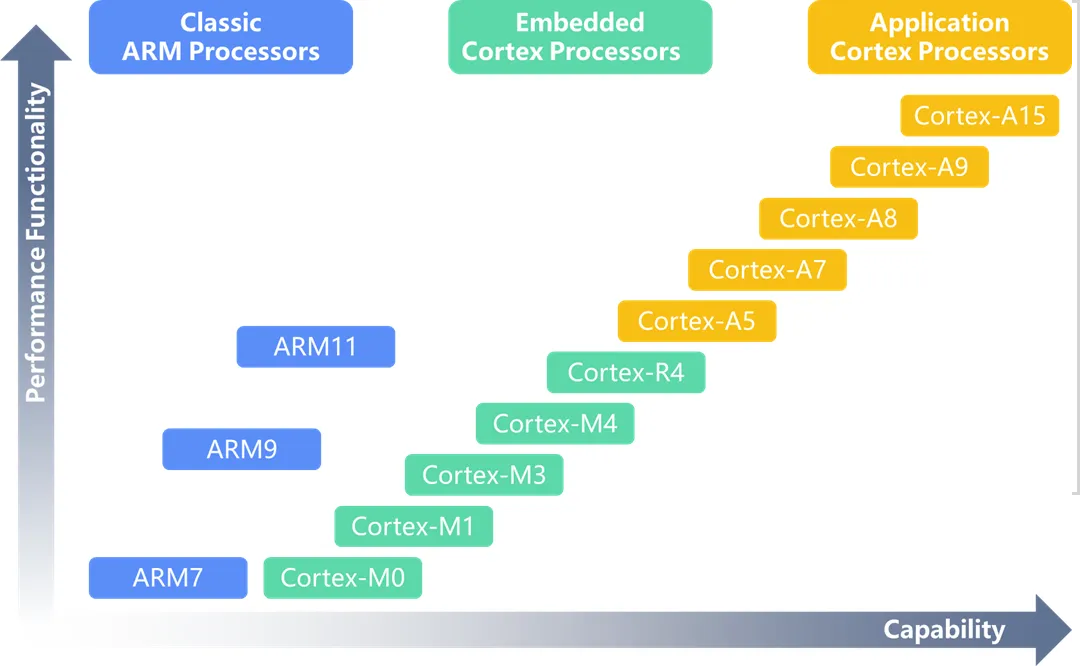

Cortex系列属于ARMv7架构(ARM公司在经典处理器ARM11以后的产品改用Cortex命名)。包括Cortex-A、Cortex-M、Cortex-R等产品。

其中:

Cortex-A系列是面向尖端的基于虚拟内存的操作系统和用户应用而设计的内核架构,通常A系列的计算能力较高,能够机型复杂的计算机图形计算,大部分使用在手机、平板和个人电脑领域。

Cortex-R系列实时处理器为要求可靠性、高可用性、容错功能、可维护性和实时响应的嵌入式系统提供高性能计算解决方案,一般用于自动驾驶、工控系统和医疗系统等。

Cortex-X系列采用了大核设计,大幅度提升内核计算能力,一般为服务器使用。

Cortex-M系列则是专门为微控制器所设计,采用了精简指令集和流水线结构,部分还具有超流水线等技术,专门为实时性、功耗、安全级别等要求较高的MCU使用。

下图为主流Cortex系列产品性能天梯图。

在车规嵌入式领域,MCU使用的较多的ARM架构就是Cortex-M系列,自2004年首款Cortex-M处理器发布以来,Cortex-M系列已经发展出多个型号,包括Cortex-M0、Cortex-M0+、Cortex-M1、Cortex-M3、Cortex-M4、Cortex-M7、Cortex-M23、Cortex-M33、Cortex-M35P和Cortex-M55等,比较典型的芯片是STM32系列、恩智浦LPC系列等。

Cortex-M有以下特色:

低功耗设计:Cortex-M系列处理器核心被设计为低功耗架构,适用于移动电源和电池供电的嵌入式系统。

高性能处理:Cortex-M处理器具有高性能的特点,能够处理复杂的实时任务,并拥有较高的处理性能。

成本效益:Cortex-M处理器提供了高性价比的解决方案,适用于各种规模的嵌入式系统设计。

处理器核心:Cortex-M处理器核心采用深层流水线和精简指令集,旨在提供高性能的处理能力。

中断控制器:Cortex-M处理器内置了灵活的中断控制器,能够支持多种中断优先级和高效的中断处理机制。

访问控制单元(ACU):ACU提供了对存储器和外设的访问控制,以保证系统的安全性和稳定性。

时钟和电源管理单元:Cortex-M处理器内置了丰富的时钟和电源管理功能,可提供灵活的功耗管理和时钟控制。

外设接口:支持多种外设接口,如UART、SPI、I2C等,以便与外部设备进行通信。

指令集:Cortex-M系列处理器支持ARM Thumb指令集,包括16位和32位的Thumb-2指令集,以及可选的DSP指令和浮点单元,提供了高性能的信号处理能力。

开发支持:设计人员可从ARM生态系统的许多工具中选择,或者使用单一、全面的工具链支持所有Cortex-M器件。

架构扩展:ARM还提供了一系列的架构扩展用于满足下一代处理器的需求,如DSP扩展、SIMD指令、浮点单元和Helium技术,为特定应用场景提供了额外的功能和性能。

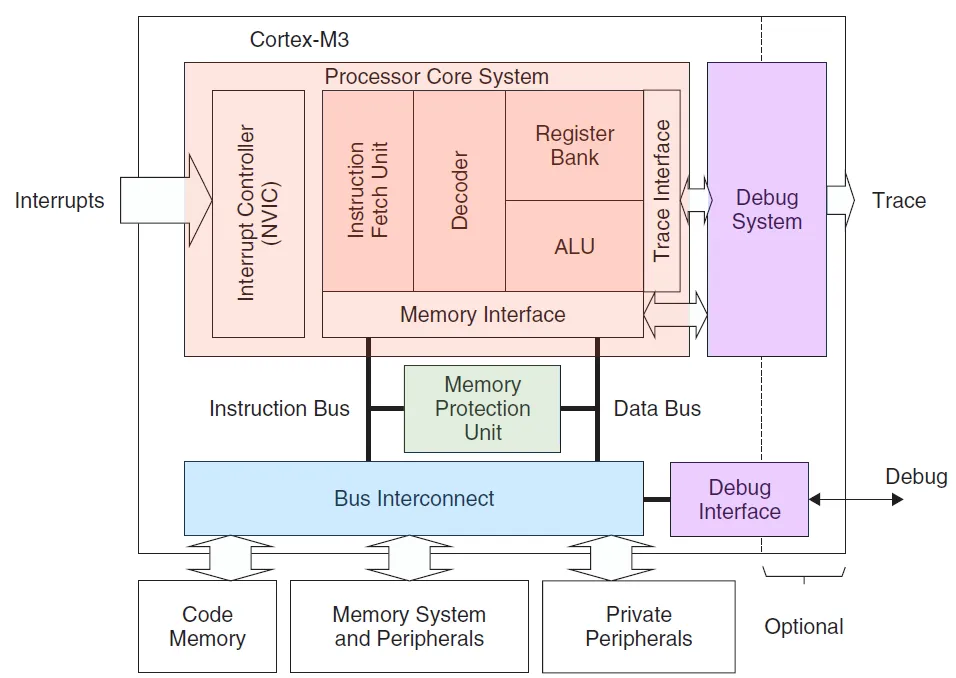

下图为Cortex-M3内核架构图。从图中我们可以看出,Cortex-M内核带有取指单元、寄存器单元、逻辑运算单元、向量中断控制器、内存接口等。采用代码、数据隔离的哈弗存储结构,是比较典型的计算机内核架构。

Cortex-M系列所用的ArmV7-M指令集,采用的是典型的load-store结构指令系统,采用32位指令系统,同时支持16位thumb指令。除了常规的运算指令,还支持查表跳转指令、条件执行、硬件除法指令、乘加指令(MAC)和各种位操作指令,其中Cortex-M7增加了基于FPv5的浮点数据架构,支持额外的浮点指令和可选的双精度浮点数据处理指令。Cortex-M7采用6级双发射流水线,提供了更高的性能。

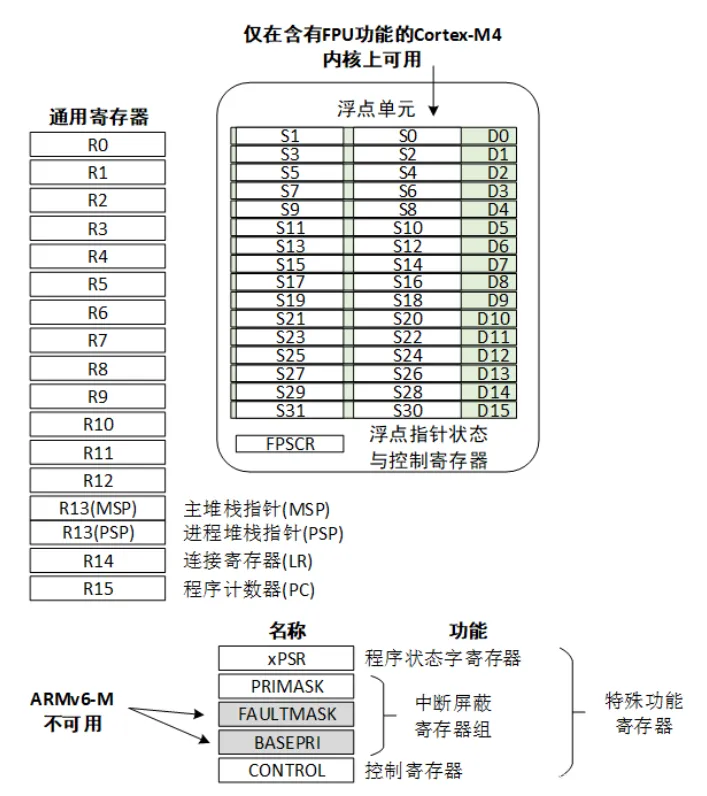

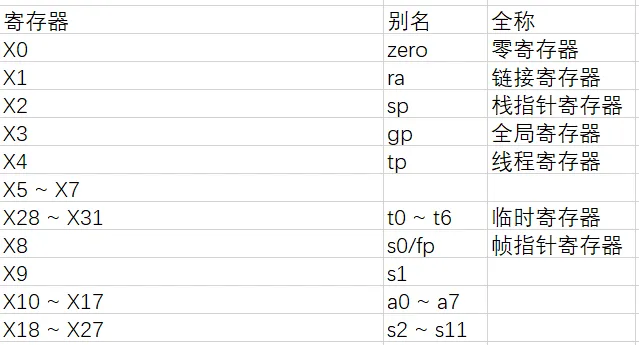

寄存器方面Cortex-M采用16个通用寄存器,和包括程序状态寄存器xPSR、控制寄存器等在内的特殊功能寄存器。

在内核架构领域,除了Intel,ARM可以说是历史最悠久的厂商了,数年来的发展奠定了行业的领先地位,基本上是授权内核IP的不二之选。不管是在嵌入式领域还是在移动领域,ARM都具有非常完备的用户生态,这在芯片领域是至关重要的,因为它意味着较低的开发和风险成本。

3.3 英飞凌TriCore内核

除了ARM这种授权内核以外,有些厂商也会进行自主内核研发,通常是实力雄厚的芯片大厂,比如瑞萨和英飞凌,就是其中的代表。这里我们以英飞凌为例介绍其TriCore内核。

英飞凌(Infineon Technologies)是一家全球领先的半导体科技公司,总部位于德国,成立于1999年,是西门子集团的半导体部门拆分出来的公司。作为一家技术领域较广的芯片厂商,其产品线包括功率MOSFET、IGBT、微控制器、传感器、射频芯片等。

在微控制器领域,英飞凌的TC2XX系列、TC3XX系列芯片为大家广泛熟知,在三电、底盘、智驾等领域具有比较高的市场占用率。包括年中刚发布的TC4XX系列,都是汽车行业的主流选择。

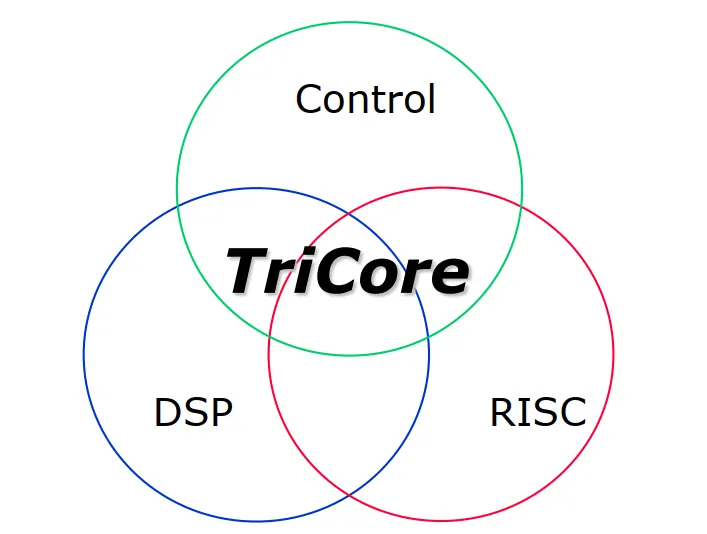

英飞凌Aurix2G TC系列芯片的内核架构是一种混合架构,同时结合了精简指令集计算机(RISC)和复杂指令集计算机(CISC)的特征,称为TriCore内核架构(以下简称TriCore)。它是一款专门为实时性进行了优化的32位的单核(这里的单核并非指芯片的单核,而是系统架构只涉及一个核,多核之间相互独立,区别于多核架构)嵌入式系统架构。之所以命名为TriCore,是因为其集成了RISC架构、DSP架构和实时系统的技术于一体,形成了兼具三方优势的内核架构。

TriCore架构采用了RISC的高性能load/store数据处理模式,同时具有DSP的数据处理能力。TriCore是32位计算机系统,因此采用32位地址空间,支持可选的虚拟地址空间。

下面是TriCore架构的特性:

•32位架构

•4GB的地址空间

•同时支持16位和32位指令,减少代码大小

•大多数指令在一个周期内执行

•分支指令(使用分支预测)

•使用并行数据存储器,实现低中断延迟与快速自动上下文切换

•专用接口特定于应用程序的协处理器,以允许添加定制指令

•零开销回路功能

•双/单时钟周期,16x16位乘法累加单元(可选饱和)

•可选浮点单元(FPU)和内存管理单元(MMU)

•广泛的位处理能力

•单指令多数据(SIMD)打包数据操作(2x16位或4x 8位操作数)

•灵活的中断优先级方案

•字节和位寻址

•数据内存和CPU寄存器的小端字节排序

•内存保护

•调试支持

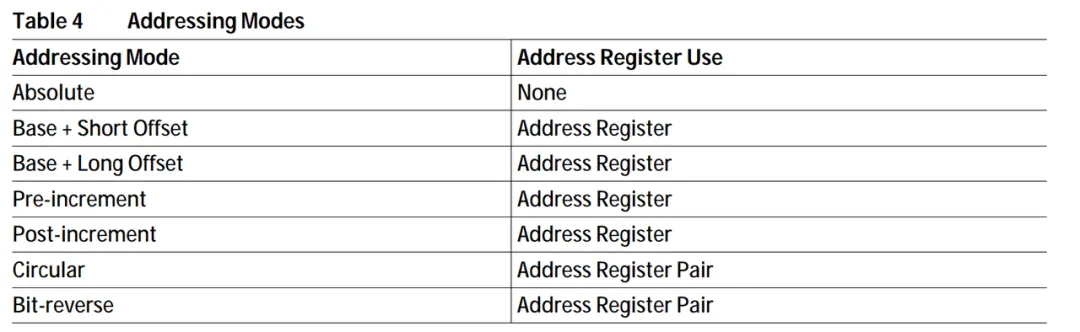

其内核为32位数据格式,支持C语言中各种基础数据类型,地址模式采用小端对齐,支持以下寻址模式。

相比于ARM内核,TriCore有两类通用寄存器,包括16个32位数据寄存器(D[0]~D[15])和16个32位地址寄存器(A[0]~A[15]),数据和地址寄存器的分离促进了算术和内存操作并行执行的高效实现。同时,相邻的两个奇偶寄存器还可以成对进行访问。

特殊功能寄存器则包括程序计数器PC、程序状态寄存器PSW、前一个上下文寄存器PCXI和系统控制寄存器。

在ARM中,上下文的内容都是保存在栈中的,当程序进行调用时,将通用寄存器和链接寄存器等压入栈中,等到调用返回时,再从栈中弹出,形成一个上下文保存机制。而TriCore内核独创了一种硬件上下文切换机制,上下文是保存在称为CSA的一片区域中的,虽然和栈一样都在RAM中,但是得益于和栈的区分式管理,以及CSA的硬件自动切换机制,能够有效地提高内存使用效率和实时性,以及安全性。

TriCore的指令集采用的也是典型的load-store结构,TriCore指令集支持32位指令和16位指令,支持嵌入式常用的微控制器系列处理指令,也支持一些DSP数据处理指令。相对于ARM,其指令结构要略复杂一些。

近年来英飞凌持续深耕汽车市场,不断推陈出新,发布符合当下电子电器架构设计以及市场需求的汽车MCU芯片,在车规MCU领域有着不可替代的地位。同时英飞凌也不断努力扩展用户生态,包括举办开发者大会、技术峰会,以及和国内高校合作等,这也非常值得国内芯片厂商借鉴和学习。

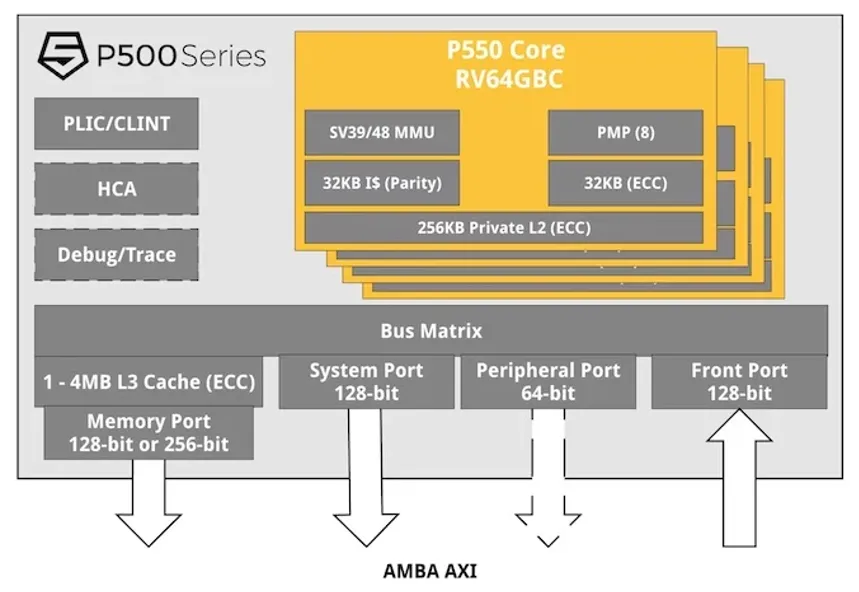

3.4 RISC-V内核

最后一类内核就是开源内核了,其中的代表就是被大家广泛采用于自研的RISC-V内核。ARM虽然授权方便,但毕竟面临着国际政治形式的影响,以及授权费。因此国内芯片一个比较热门的技术路线,就是基于开源RISC-V进行自研。

RISC-V是一种开源的指令集架构,起源于加州大学伯克利分校的研究项目。RISC-V是RISC架构的第五代内核,它的发展历史可以追溯到2010年,当时该校的研究团队为了设计一款CPU,对比了现有的ARM、MIPS、SPARC和x86等指令集,发现它们不仅复杂,还涉及许多知识产权问题。因此,研究团队决定开发一套全新的指令集,这就是RISC-V的起源。

随着技术的发展,RISC-V在嵌入式系统、物联网、AIOT等领域的应用越来越广泛,许多企业和研究机构开始采用RISC-V进行产品开发和研究。它的开源特性为全球芯片设计者提供了一个没有限制、可以自由发挥的平台,预示着RISC-V在未来的技术发展中将扮演越来越重要的角色。

下图为SiFive公司的一款RISC-V处理器框图。

RISC-V有以下特点:

模块化设计:RISC-V架构采用模块化设计,允许用户根据具体需求选择适合的模块进行组合,实现定制化的处理器设计。

开源性:RISC-V架构的开源性意味着任何人都可以查看、修改和分发RISC-V架构的源代码,这促进了广泛的支持和发展。

灵活性:RISC-V架构支持多种指令集扩展,如向量指令、浮点指令等,使得处理器可以适应不同的应用场景。

降低成本:开源性使用户可以免费使用RISC-V架构,降低了处理器的研发成本。

高性能:RISC-V采用精简指令集设计,具有简单、高效的特点,同时模块化设计允许优化处理器结构,提高性能。

增强安全性:RISC-V架构具有强大的安全特性,如硬件级别的隔离、加密和防篡改等。

RISC-V的指令集包括如下类型:

R类型(寄存器-寄存器操作);

I类型(立即数操作);

S类型(存储操作);

B类型(分支操作);

U类型(上位操作);

J类型(跳转操作);

C类型(压缩操作);

F类型(浮点操作);

其指令格式相对比较简洁,比如ADD rd, rs1, rs2(将rs1和rs2的值相加,结果存储在rd中)。

RISC-V的指令格式设计使得它能够高效地在现代处理器中执行,同时保持了足够的灵活性来支持各种不同的计算任务。这种设计哲学是RISC-V受欢迎的重要原因之一。

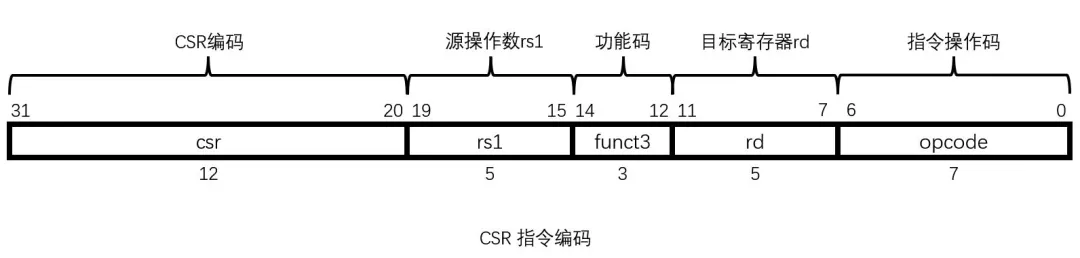

RISC-V的寄存器包括32个通用寄存器,和一系列控制状态寄存器(CSR)。

2023年3月2日,在玄铁RISC-V生态大会上,工程院院士倪光南表示,基于RISC-V模块化、可扩展、容易定制、不受垄断制约等优势,成为了中国CPU领域最受欢迎的架构。

而芯来科技于2020年发布了32位RISC-V架构的NA900系列处理器,并于2023年获得了ISO

26262最高汽车功能安全等级ASIL D的产品认证,也是国内首家获得该认证的CPU IP提供商。也是继ARM、Synopsys之后,全球第三家获得车规ISO

26262 ASIL D产品认证的CPU IP提供商。

但目前来说,RISC-V内核在车规MCU领域应用还比较少,具有比较大的发展空间。

#04 小 结

当今嵌入式领域中,主流的授权模式内核还是ARM系列,这也是国内外芯片厂商选择最多的IP,也有一些厂商选择Synopsys的车规MCU内核。一些厂商如英飞凌、瑞萨等具有内供自研内核,且相应的芯片在车规领域占有较大的市场。而开源内核架构RISC-V异军突起,被国内外在自研领域有布局的厂商所青睐。

|