|

简介

在 FPGA 中,可以根据功能需求灵活的定制数字电路,实现面向硬件的功能逻辑编程。 VHDL 是 FPGA 的开发语言,可以根据功能逻辑设计,编写相应的程序,然后生成 FPGA 的数字电路,实现相应的功能。

FPGA 实现的功能具有高效的性能,而且还能够根据需求进行灵活的定制,在实时性要求高的嵌入式系统中应用越来越广泛。 FPGA 应用的功能也越来愈复杂,所以有必要进行建模 FPGA 应用的功能逻辑,以便提高开发的质量和效率。

嵌入式系统的分析设计建模目前广泛采用的建模语言是 Sys ML ,可以建立需求模型、系统模型、软件模型和硬件模型。作为嵌入式系统开发的一种实现机制, FPGA 的建模需要和整个嵌入式系统的其他模型进行关联和跟踪。所以本文提出一种采用 Sys ML 进行 FPGA 功能逻辑建模,并把建立的模型映射到 VHDL 程序代码。

下面以一个全加器的设计和开发为例,介绍采用SysML对FPGA应用的功能逻辑建模的方法。

全加器的数字电路、数字信号和相关处理简介

首先,我们先看全加器的逻辑电路如下:

全加器的功能:输入信号 ain 和 bin 相加,然后和低位进位信号 cin 相加,输出进位信号 cout 和 1 位输出信号 sum 。全加器的构成: 2 个半加器和 1 个或门。

采用 Sys ML 对全加器进行逻辑建模的示例

下面采用 SysML 对全加器的功能逻辑进行建模。

首先采用 Sys ML 的模块定义图( Block Definition Diagram )对全加器包含的逻辑器件类型进行建模:

然后定义每个硬件逻辑单元的输入输出和功能,采用Sys ML的内部模块图(Internal Block Diagram)建模。为了方便理解,附上了对应的VHDL代码。下面逐一说明:

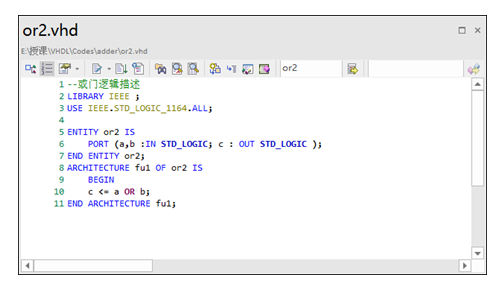

1) 或门or2的输入输出和功能采用Sys ML的内部模块图(Internal Block Diagram)建模(同时提供对应的VHDL代码):

|

或门 or2 的内容:

输入信号: a,b

输出信号: c

功能逻辑: fu1 |

|

|

|

或门 or2 的内容:

输入信号: a,b

输出信号: c

功能逻辑: fu1 |

|

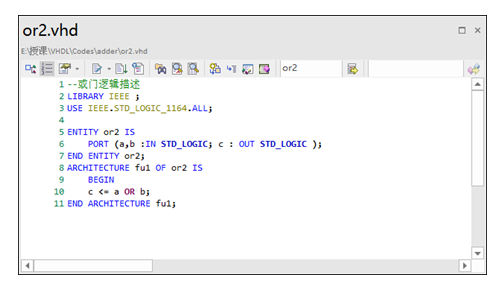

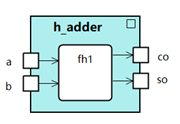

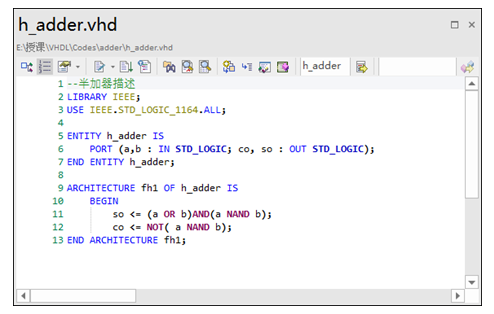

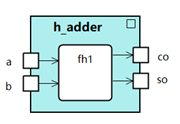

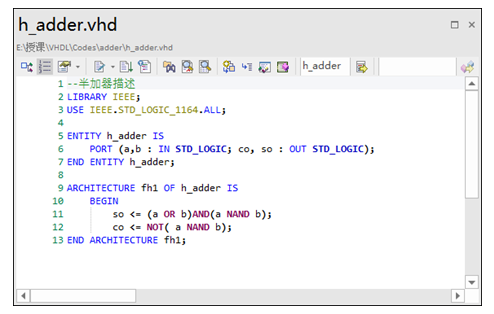

2) 半加器h_adder的输入输出和功能采用Sys ML的内部模块图(Internal Block Diagram)建模(同时提供对应的VHDL代码):

|

半加器的内容:

输入信号: a,b

输出信号:

功能逻辑: fh1

a,b 的和个位输出给 so

进位输出给 co |

|

|

|

半加器的内容:

输入信号: a,b

输出信号:

功能逻辑: fh1

a,b 的和个位输出给 so

进位输出给 co |

|

3) 全加器f_adder的输入输出和功能采用Sys ML的内部模块图(Internal Block Diagram)建模:

全加器由 2 个半加器和 1 个或门构成:

- 半加器 U1 (器件类型为 h_adder )

- 半加器 U2 (器件类型为 h_adder )

- 或门 U3 (器件类型为 or2 )

全加器的输入信号 :

- ain :相加信号

- bin :相加信号

- cin :低位进位输入;

全加器的输出信号:

- cout 为进位输出;

- sum 为 1 位和输出。

全加器的计算过程如下:

- 《ain:输入信号》和《bin:输入信号》分别为两个输入的相加位,经过《半加器:U1》相加后输出《so: 和信号》和《co:进位信号》

- 《so: 和信号》和《低位进位输入信号:cin》输入《半加器:U2》

- 《半加器:U2》输出的《so: 和信号》作为1位输出《sum》

- 《半加器:U2》输出的《co:进位信号》和《半加器:U1》输出的《co:进位信号》输入《或门:or2》进行计算,作为输出《cout》

相应的 VHDL 代码如下:

结束语

本文提出了一种采用Sys ML建模语言对FPGA功能逻辑建模的方法,并提供对应的VHDL程序代码,目的是让FPGA的开发和整个嵌入式系统开发建立关联和跟踪,实现嵌入式系统完整的MBSE。FPGA和VHDL还有很多内容有待进一步采用Sys ML进行建模,后续会继续提供相关的文章。

后记

希望您读了此文后有所受益.

如果您有经验乐于分享,欢迎投稿给我们,如果您对我们的培训、咨询和工具感兴趣,欢迎了解:

• 建模工具: EA

• MBSE 平台: iSpace

• 模型 web 浏览工具: WebEA

• 课程: 基于SysML和EA进行系统设计与建模

• 课程: 基于UML和EA进行系统分析设计

• 咨询方案: MBSE( 基于模型的系统工程 )

• 咨询方案: 基于 UML 的模型驱动的开发

• 所有建模有关的课程: http://www.modeler.org.cn/course/index.asp

• 咨询方案: 基于模型的工程管理

如果您希望了解更多信息:

作者简介:

| 俎涛,火龙果软件工程创始人, 2001 年创立了火龙果软件工程, 2004 年创立了 IBM Rational 用户组. 1998 年,曾作为骨干参与国家重点研究课题《面向特定领域基于组件的软件复用》,有幸比较深入的学习和使用的 UML 进行领域建模、提炼可复用组件和架构.在后来的研发项目中,一直采用模型进行分析设计,积累了一些心得和经验.在以往的经历中,最大的感触是汇聚了很多精英人才的软件工程和系统工程领域居然几十年都是一种凌乱迷蒙的状态,从自己的经历所得,觉得清晰的模型,才是拨开工程迷雾的关键所在,所以不断研究和应用各种建模技术,并从自己的工程实践中提炼经验,形成对于自己可持续的方法论,例如《 Nature Model Language- 自然建模语言》《基于模型的三维研发管理》《 iProcess 过程改进方法》《基于模型的需求管理》《模型驱动的架构设计》《基于模型的质量管理》《基于模型的人员能力管理》,目前正在作为产品经理和架构师,进行 MBSE (基于模型的系统工程)平台的研发,希望建立要给基于模型的工程解决方案,后续会不断写些文章,希望能给同行一些借鉴.

|

|