| БрМЭЦМі: |

БОЮФРДздгкcsdnЃЌOTAЙЬМўЩ§МЖПЩШУПЊЗЂШЫдБЫцзХЪБМфЕФЭЦвЦдіЧПВњЦЗЙІФмЃЌВЂаоВЙВњЦЗШБЯнЁЃзюКѓЃЌбЁдёПЩТњзуФњЕФгІгУашЧѓ,ИќЖрЯъЯИФкШнЧыдФЖСЯТЮФЁЃ |

|

аэЖрЧЖШыЪНЯЕЭГВПЪ№дкШЫРрВйзїдБКмФбЛђЮоЗЈЗУЮЪЕФЕиЗНЁЃ ЖдгкЮяСЊЭјгІгУГЬађРДЫЕгШЦфШчДЫЃЌЮяСЊЭјгІгУГЬађЭЈГЃЪ§СПНЯДѓЃЌЕчГиЪйУќгаЯоЁЃ

вЛаЉР§згЪЧМрЪгШЫЛђЛњЦїНЁПЕзДПіЕФЧЖШыЪНЯЕЭГЁЃ етаЉЬєеНЃЌдйМгЩЯПьЫйЕФШэМўЩњУќжмЦкЃЌЕМжТаэЖрЯЕЭГашвЊЖдOTAИќаТЬсЙЉжЇГжЁЃ

OTAИќаТвдаТЕФШэМўЬцДњСЫЧЖШыЪНЯЕЭГжаЕЅЦЌЛњЛђЮЂДІРэЦїЩЯЕФШэМўЁЃ

ЫфШЛаэЖрШЫЗЧГЃЪьЯЄЫћУЧЕФвЦЖЏЩшБИЩЯЕФ OTA ИќаТЃЌЕЋЪЧдкзЪдДЪмЯоЕФЯЕЭГЩЯЕФЩшМЦКЭЪЕЯжЛсДјРДаэЖрВЛЭЌЕФЬєеНЁЃ

дкIoTЙЬ/ШэМўИќаТМАПЊдДбЁЯювЛЮФжаЃЌбЇЯАСЫвЛаЉПЊдДЕФММЪѕЃЌдкетРяЃЌНЋУшЪіМИжжВЛЭЌЕФOTAИќаТШэМўЩшМЦЃЌВЂЬжТлЫќУЧЕФРћБзЃЌВЂНЋСЫНтСНИіГЌЕЭЙІКФЮЂПижЦЦїЕФгВМўЬиадШчКЮдк

OTAИќаТШэМўжаЕУЕНЕФРћгУЁЃ

ЙЙНЈЛљДЁ

ЧЖШыЪНЯЕЭГжаЕФCSМмЙЙ

OTAЩ§МЖгУаТЕФШэМўШЁДњСЫЩшБИЩЯЯжгаЕФШэМўЃЌаТЕФШэМўЭЈЙ§ЮоЯпЭјТчЯТдиЁЃ

дкЧЖШыЪНЯЕЭГжаЃЌдЫааетИіШэМўЕФЩшБИЭЈГЃЪЧвЛИіЮЂПижЦЦїЁЃ ЮЂПижЦЦїЪЧвЛжжаЁаЭМЦЫуЩшБИЃЌОпгагаЯоЕФДцДЂЦїЃЌЫйЖШКЭЙІКФЁЃ

ЮЂПижЦЦїЭЈГЃАќКЌвЛИіЮЂДІРэЦї(КЫаФ)вдМАгУгкЬиЖЈВйзї(ЭтЮЇЩшБИ)ЕФЪ§зжгВМўЁЃ ГЌЕЭЙІКФЮЂПижЦЦїЭЈГЃдкжїЖЏФЃЪНЯТЯћКФ30

ЮЂАВ/MhzЕН40ЮЂАВ/MhzЃЌЪЧетжжРраЭгІгУЕФРэЯыбЁдёЁЃ

дкетаЉЮЂПижЦЦїЩЯЪЙгУЬиЖЈЕФгВМўЭтЩшЃЌВЂНЋЦфЩшжУЮЊЕЭЙІКФФЃЪНЃЌЪЧ OTA

ИќаТШэМўЩшМЦЕФживЊзщГЩВПЗжЁЃ ЭМ1ЯдЪОСЫвЛИіПЩФмашвЊ OTA ИќаТЕФЧЖШыЪНЯЕЭГЪОР§ЁЃ етРяЕФвЛИіЮЂПижЦЦїСЌНгзХвЛИіЮоЯпФЃПщКЭДЋИаЦїЃЌЫќПЩвдгУдкЮяСЊЭјгІгУжаЃЌЭЈЙ§ДЋИаЦїЪеМЏЛЗОГЪ§ОнЃЌВЂЖЈЦкгУЮоЯпФЃПщБЈИцЁЃ

ЯЕЭГЕФетвЛВПЗжГЦЮЊБпдЕНкЕуЛђПЭЛЇЖЫЃЌЪЧ OTA ИќаТЕФФПБъЁЃ ЯЕЭГЕФСэвЛВПЗжГЦЮЊдЦЛђЗўЮёЦїЃЌЪЧаТШэМўЕФЬсЙЉепЁЃ

ЗўЮёЦїКЭПЭЛЇЖЫЭЈЙ§ЪЙгУЪеЗЂаХЛњ(ЮоЯпЕч)НјааЭЈаХЁЃ

ЭМ1 ЧЖШыЪНЯЕЭГжаЕФПЭЛЇЛњ/ЗўЮёЦїЬхЯЕНсЙЙ

OTA ЕФШэМўБОжЪ

OTAИќаТСїГЬЕФДѓВПЗжЙЄзїЪЧНЋаТШэМўДгЗўЮёЦїзЊвЦЕНПЭЛЇЖЫЁЃ ЕБШэМўДгдДДњТыИёЪНзЊЛЛЮЊЖўНјжЦИёЪНКѓЃЌШэМўвдзжНкађСаЕФаЮЪНДЋЪфЁЃ

зЊЛЛЙ§ГЬАќРЈБрвыдДДњТыЮФМў(Р§Шч cЁЂ cpp) ЃЌНЋЫќУЧСДНгЕНвЛИіПЩжДааЮФМў(Р§Шч exeЁЂ elf)жаЃЌШЛКѓНЋПЩжДааЮФМўзЊЛЛЮЊПЩвЦжВЕФЖўНјжЦЮФМўИёЪН(Р§Шч

binЁЂ hex)ЁЃетаЉЮФМўИёЪНАќКЌвЛИізжНкађСаЃЌЪєгкЮЂПижЦЦїФкДцЕФЬиЖЈЕижЗЁЃ?

ЭЈГЃЃЌЭЈЙ§ЮоЯпСДТЗЗЂЫЭЕФаХЯЂИХФюЛЏЮЊЪ§ОнЃЌР§ШчИќИФЯЕЭГзДЬЌЛђЯЕЭГЪеМЏЕФДЋИаЦїЪ§ОнЕФУќСюЁЃ

дк OTA ИќаТЕФЧщПіЯТЃЌЪ§ОнЪЧЖўНјжЦИёЪНЕФаТШэМўЁЃ дкаэЖрЧщПіЯТЃЌЖўНјжЦЮФМўЬЋДѓЃЌЮоЗЈНЋвЛДЮДЋЪфДгЗўЮёЦїЗЂЫЭЕНПЭЛЇЛњЃЌетвтЮЖзХашвЊНЋЖўНјжЦЮФМўЗХШыЕЅЖРЕФЪ§ОнАќжаЃЌетИіЙ§ГЬБЛГЦЮЊДђАќЁЃ

ЮЊСЫИќКУЕиНЋетвЛЙ§ГЬПЩЪгЛЏЃЌЭМ2бнЪОСЫВЛЭЌАцБОЕФШэМўШчКЮЩњГЩВЛЭЌЕФЖўНјжЦЮФМўЃЌДгЖјдк OTA ИќаТЦкМфЗЂЫЭВЛЭЌЕФЪ§ОнАќЁЃ

дкетИіМђЕЅЕФЪОР§жаЃЌУПИіЪ§ОнАќАќКЌ8ИізжНкЕФЪ§ОнЃЌЧА4ИізжНкБэЪОПЭЛЇЛњФкДцжаЕФЕижЗЃЌгУгкДцДЂКѓ4ИізжНкЕФЪ§ОнЁЃ

ЭМ2 ШэМўгІгУЕФЖўНјжЦзЊЛЛКЭДђАќЙ§ГЬ

OTAЕФжївЊЬєеН

ЛљгкетжжЖд OTA ИќаТСїГЬЕФУшЪіЃЌOTA ИќаТНтОіЗНАИБиаыНтОіШ§ДѓЬєеНЁЃ

ЕквЛИіЬєеНгыФкДцгаЙиЁЃ ШэМўНтОіЗНАИБиаыНЋаТЕФШэМўгІгУГЬађзщжЏЕНПЭЛЇЖЫЩшБИЕФвзЪЇадЛђЗЧвзЪЇадДцДЂЦїжаЃЌвдБудкИќаТЙ§ГЬЭъГЩЪБжДааЁЃ

НтОіЗНАИБиаыШЗБЃвдЧАЕФШэМўАцБОдкаТШэМўГіЯжЮЪЬтЪБзїЮЊКѓБИгІгУГЬађБЃСєЯТРДЁЃ ДЫЭтЃЌБиаыБЃСєПЭЛЇЖЫЩшБИЕФзДЬЌжЎМфЕФжижУКЭЕчдДжмЦкЃЌШчШэМўЕФАцБОЃЌвбОФПЧАе§дкдЫаадкФкДцжаЕФЮЛжУЁЃ

ЕкЖўИіЬєеНЪЧЭЈаХЁЃаТШэМўБиаывдРыЩЂЪ§ОнАќЕФаЮЪНДгЗўЮёЦїЗЂЫЭЕНПЭЛЇЛњЃЌУПИіЪ§ОнАќеыЖдПЭЛЇЛњФкДцжаЕФЬиЖЈЕижЗЁЃ

ШэМўЩшМЦжаБиаыПМТЧЪ§ОнАќЕФЗжзщЗНАИЁЂЗжзщНсЙЙКЭДЋЪфавщЁЃ

зюКѓвЛИіжївЊЬєеНЪЧАВШЋЮЪЬтЁЃ ЫцзХаТЕФШэМўДгЗўЮёЦїЮоЯпЗЂЫЭЕНПЭЛЇЖЫЃЌБиаыШЗБЃЗўЮёЦїЪЧПЩаХЕФЁЃ

етжжАВШЋЬєеНГЦЮЊЩэЗнбщжЄЃЌЛЙБиаыШЗБЃаТШэМўЖдШЮКЮЙлВьепНјааФЃК§ДІРэЃЌвђЮЊЫќПЩФмАќКЌУєИааХЯЂЁЃетжжАВШЋЬєеНГЦЮЊБЃУмадЁЃ

АВШЋЕФзюКѓвЛИівЊЫиЪЧЭъећадЃЌШЗБЃаТШэМўдкПежаЗЂЫЭЪБВЛЛсЫ№ЛЕЁЃ

в§ЕММгдиГЬађ

РэНтЦєЖЏЫГађ

жїв§ЕММгдиГЬађЪЧгРОУзЄСєдкЮЂПижЦЦїжЛЖСФкДцЩЯЕФШэМўгІгУГЬађЁЃ жїв§ЕММгдиГЬађзЄСєЕФФкДцЧјгђГЦЮЊаХЯЂПеМфЃЌгУЛЇгаЪБЮоЗЈЗУЮЪИУЧјгђЁЃ

етИігІгУГЬађдкУПДЮжижУЪБжДааЃЌЭЈГЃжДаавЛаЉБивЊЕФгВМўГѕЪМЛЏЃЌВЂПЩФмМгдигУЛЇШэМўЕНФкДцжаЁЃ

ЕЋЪЧЃЌШчЙћЕЅЦЌЛњАќКЌЦЌФкЗЧвзЪЇадФкДцЃЌШчЩСДцЃЌЦєЖЏМгдиГЬађВЛашвЊзіШЮКЮМгдиЃЌжЛашНЋПижЦШЈзЊвЦЕНЩСДцжаЕФГЬађЁЃ

ШчЙћжїв§ЕММгдиГЬађУЛгаЖд OTA ИќаТЕФШЮКЮжЇГжЃЌдђгаБивЊЪЙгУЕкЖўНзЖЮв§ЕММгдиГЬађЃЈSSBLЃЉЁЃ гыжїв§ЕММгдиГЬађвЛбљЃЌSSBL

НЋдкУПДЮresetЪБдЫааЃЌЕЋНЋЪЕЯжOTAИќаТЙ§ГЬЕФвЛВПЗжЁЃ в§ЕМЫГађШчЭМ3ЫљЪОЁЃ дкетРяНЋбЇЯАЮЊЪВУДашвЊЕкЖўНзЖЮв§ЕММгдиГЬађЃЌвдМАШчКЮжИЖЈДЫгІгУГЬађЕФНЧЩЋЪЧвЛИіЙиМќЕФЩшМЦШЈКтЁЃ

ЭМ3 гУSSBLЪЕЯжФкДцгГЩфКЭв§ЕМСїЕФЪОР§

ВЛЪЙгУSSBLЕФЮЪЬт

ДгИХФюЩЯНВЃЌЪЁТд SSBL НЋЫљгаЕФOTAИќаТЙІФмЗХЕНгУЛЇгІгУГЬађжаЫЦКѕИќМђЕЅЃЌвђЮЊЫќНЋдЪаэЯжгаЕФШэМўПђМмЁЂВйзїЯЕЭГКЭЩшБИЧ§ЖЏГЬађЮоЗьЕигУгкOTAЙ§ГЬЁЃ

бЁдёетжжЗНЗЈЕФЯЕЭГФкДцгГЩфКЭв§ЕМЫГађШчЭМ4ЫљЪОЁЃ

ЭМ4 УЛгаSSBLЕФФкДцгГЩфКЭЦєЖЏСї

гІгУГЬађAЪЧдРДЕФгІгУЃЌЪЧВПЪ№дкЮЂПижЦЦїЕФПижЦгђЁЃ ДЫгІгУГЬађАќКЌгы

OTA ИќаТЯрЙиЕФШэМўЃЌЕБЗўЮёЦїЧыЧѓЪБЃЌНЋРћгУИУШэМўЯТдигІгУГЬађ BЁЃ дкЭъГЩЯТдиВЂбщжЄСЫгІгУГЬађB

жЎКѓЃЌгІгУГЬађAНЋЭЈЙ§ЯђгІгУГЬађBжДааresetжИСюНЋПижЦзЊвЦЕНгІгУГЬађBЁЃ resetДІРэГЬађЪЧвЛаЁЖЮДњТыЃЌЫќЪЧШэМўгІгУГЬађЕФШыПкЕуЃЌВЂдкжижУЪБдЫааЁЃ

дкетжжЧщПіЯТЃЌЭЈЙ§жДааЗжжЇ(ЯрЕБгкКЏЪ§ЕїгУ)РДФЃЗТresetЁЃ

етжжзіЗЈгаСНИіжївЊЮЪЬт:

аэЖрЧЖШыЪНШэМўгІгУГЬађЪЙгУЪЕЪБВйзїЯЕЭГ(RTOS) ЃЌЫќдЪаэНЋШэМўЗжНтГЩВЂЗЂШЮЮёЃЌУПИіШЮЮёдкЯЕЭГжагаВЛЭЌЕФжАд№ЁЃ

Р§ШчЃЌЭМ1ЫљЪОЕФгІгУГЬађПЩФмОпгаЖСШЁДЋИаЦїЁЂдкДЋИаЦїЪ§ОнЩЯдЫааЫуЗЈвдМАгыЮоЯпФЃПщСЌНгЕФ RTOS ШЮЮёЁЃ

RTOSБОЩэзмЪЧДІгкЛюЖЏзДЬЌЃЌИКд№ЛљгквьВНЪТМўЛђЬиЖЈЕФЪБМфбгГйдкетаЉШЮЮёжЎМфЧаЛЛЁЃ вђЮЊЦфЫћШЮЮёНЋБЃГждкКѓЬЈдЫааЃЌЫљвдДг

RTOS ШЮЮёЗжжЇЕНвЛИіаТЕФГЬађЪЧВЛАВШЋЕФЃЌ ЮЈвЛАВШЋЕФЗНЗЈЪЧЭЈЙ§ЭЈЙ§жижУРДжежЙвЛИіГЬађгыЪЕЪБВйзїЯЕЭГЁЃ

ЛљгкЭМ4ЃЌНтОіЩЯвЛИіЮЪЬтЕФАьЗЈЪЧНЋжїв§ЕММгдиГЬађЧаЛЛЕНгІгУГЬађBЃЌЖјВЛЪЧгІгУГЬађAЁЃШЛЖјЃЌдквЛаЉЮЂПижЦЦїЩЯЃЌжїв§ЕММгдиГЬађзмЪЧдЫаажаЖЯЯђСПБэ(IVT)ЕФГЬађЃЌIVT

ЪЧгІгУГЬађжаУшЪіжаЖЯДІРэКЏЪ§ЕФЙиМќВПЗжЃЌЮЛгкЕижЗ0ЁЃ етвтЮЖзХашвЊФГжжаЮЪНЕФIVTжиаТЖЈЮЛЕНгІгУГЬађBЕФжижУгГЩфЁЃ

ШчЙћЕчдДжиЦєдк IVT жиаТЖЈЮЛЙ§ГЬжаЗЂЩњЃЌдђПЩФмЪЙЯЕЭГДІгкгРОУадЕФЦЦЛЕзДЬЌЁЃ

ШчЭМ3ЫљЪОЃЌЭЈЙ§дкЕижЗ0ДІЩшжУ SSBL ПЩвдМѕЧсетаЉЮЪЬтЁЃ гЩгкSSBLЪЧвЛИіЗЧRTOSГЬађЃЌЫќПЩвдАВШЋЕиЧаЛЛЕНвЛИіаТЕФгІгУГЬађЁЃЮоашЖдЕчдДжиЦєЙизЂЃЌвђЮЊ

IVT ЕФ SSBL дкЕижЗ0ЪЧДгРДУЛгажижУЕФЁЃ

SSBL ЕФЙІФм

СЫНтСЫ SSBL МАЦфгыгІгУШэМўЕФЙиЯЕЃЌФЧетИі SSBL зіЪВУДФиЃП

зюЦ№ТыЃЌГЬађБиаыШЗЖЈЕБЧАгІгУГЬађЪЧЪВУД(ПЊЪМЕФЮЛжУ) ЃЌШЛКѓдйЧаЛЛЕНИУЕижЗЁЃ ШчЭМ3ЫљЪОЃЌЮЂПижЦЦїФкДцжаИїжжгІгУГЬађЕФЮЛжУЭЈГЃБЃДцдквЛИіФПТМ(ToC)жаЁЃ

етЪЧГжОУФкДцЕФвЛИіЙВЯэЧјгђЃЌSSBLКЭгІгУГЬађШэМўЖМЪЙгУЫќУЧРДЯрЛЅЭЈаХЁЃ

ЕБ OTA ИќаТЙ§ГЬЭъГЩЪБЃЌToC НЋЪЙгУаТЕФгІгУГЬађаХЯЂНјааИќаТЁЃ

OTAИќаТЙІФмЕФвЛВПЗжвВПЩвдЭЦЫЭЕНSSBLЁЃдкПЊЗЂ OTA ИќаТШэМўЪБЃЌЁАШЗЖЈФФаЉВПЗжЁБЪЧвЛИіживЊЕФЩшМЦОіВпЁЃ

ЩЯУцУшЪіЕФзюаЁ SSBL НЋЪЧЗЧГЃМђЕЅЕФЃЌвзгкбщжЄЃЌВЂЧвКмПЩФмВЛашвЊдкгІгУГЬађЕФЩњУќжмЦкжаНјаааоИФЁЃ

ЕЋЪЧЃЌетвтЮЖзХУПИігІгУГЬађБиаыИКд№ЯТдиВЂбщжЄЯТвЛИігІгУГЬађЁЃ етПЩФмЕМжТЮоЯпЖбеЛЁЂЩшБИЙЬМўКЭ

OTA ИќаТШэМўЗНУцЕФДњТыжиИДЁЃ СэвЛЗНУцЃЌПЩвдбЁдёНЋећИі OTA ИќаТЙ§ГЬЭЦЫЭЕН SSBLЁЃ дкетжжЧщПіЯТЃЌгІгУГЬађжЛашдк

ToC жаЩшжУвЛИіБъжОРДЧыЧѓИќаТЃЌШЛКѓжДааИДЮЛЁЃ SSBLШЛКѓжДааЯТдиађСаКЭбщжЄЙ§ГЬЁЃ етНЋзюДѓЯоЖШЕиМѕЩйДњТыжиИДЃЌВЂМђЛЏгІгУГЬађЬиЖЈЕФШэМўЁЃ

етДјРДСЫвЛИіаТЕФЬєеНЃЌПЩФмашвЊИќаТ SSBL БОЩэ(МДЩ§МЖИќаТДњТы)ЁЃ

зюКѓЃЌОіЖЈдк SSBL жаЗХжУЪВУДЙІФмНЋШЁОігкПЭЛЇЖЫЩшБИЕФФкДцдМЪјЁЂЯТдигІгУГЬађжЎМфЕФЯрЫЦадвдМА OTA

ИќаТШэМўЕФПЩвЦжВадЁЃ

ЩшМЦШЈКт: ЛКДцКЭбЙЫѕ

OTAИќаТШэМўжаЕФСэвЛИіЙиМќЩшМЦОіВпЪЧдк OTA ИќаТЙ§ГЬжаШчКЮдкФкДцжазщжЏЪеЕНЕФгІгУГЬађЁЃ

ЮЂПижЦЦїжаСНжжЕфаЭЕФДцДЂЦїЪЧЗЧвзЪЇадДцДЂЦї(Р§ШчЃЌЩСДц)КЭвзЪЇадДцДЂЦї(Р§ШчЃЌSRAM)ЁЃ ЩСДцНЋгУгкДцДЂГЬађДњТыКЭгІгУГЬађЕФжЛЖСЪ§ОнЃЌвдМАЦфЫћЯЕЭГМЖЪ§ОнЃЌШч

ToC КЭЪТМўШежОЁЃ SRAMНЋгУгкДцДЂШэМўгІгУГЬађЕФПЩаоИФВПЗжЃЌР§ШчЗЧГЃСПШЋОжБфСПКЭЖбеЛЁЃ ЭМ2ЫљЪОЕФШэМўгІгУГЬађЖўНјжЦДњТыжЛАќКЌГЬађдкЗЧвзЪЇадДцДЂЦїжаЕФВПЗжЁЃ

дкЦєЖЏР§ГЬЦкМфЃЌгІгУГЬађНЋГѕЪМЛЏЪєгкПЩБфФкДцжаЕФВПЗжЁЃ

дк OTA ИќаТЙ§ГЬжаЃЌУПЕБПЭЛЇЖЫЩшБИДгЗўЮёЦїНгЪеЕНвЛИіАќКЌВПЗжЖўНјжЦЕФЪ§ОнАќЪБЃЌЫќНЋБЛДцДЂдк

SRAM жаЁЃ етИіЪ§ОнАќПЩвдЪЧбЙЫѕЕФЃЌвВПЩвдЪЧЮДбЙЫѕЕФЁЃ бЙЫѕгІгУГЬађЖўНјжЦЮФМўЕФКУДІЪЧЫќЕФЬхЛ§ИќаЁЃЌдЪаэЗЂЫЭЕФЪ§ОнАќИќЩйЃЌдкЯТдиЙ§ГЬжа

SRAM жаДцДЂЫќУЧЫљашЕФПеМфИќЩйЁЃ етжжЗНЗЈЕФШБЕуЪЧбЙЫѕКЭНтбЙЫѕЛсИјИќаТЙ§ГЬдіМгЖюЭтЕФДІРэЪБМфЃЌЖјЧвБиаыдк

OTA ИќаТШэМўжаРІАѓЯрЙиДњТыЁЃ

гЩгкаТЕФгІгУШэМўдкЩ§МЖЙ§ГЬжаЮЛгкЩСДцжаЃЌЕЋЪЧдкЩ§МЖЙ§ГЬжаШДНјШыСЫ

SRAMЃЌЫљвд OTA ЕФЩ§МЖШэМўдкЩ§МЖЙ§ГЬжаашвЊЖдЩСДцНјаааДВйзїЁЃ дк SRAM жаСйЪБДцДЂаТгІгУГЬађГЦЮЊЛКДцЁЃ

дкИпВуЃЌOTA ИќаТШэМўПЩвдВЩШЁШ§жжВЛЭЌЕФЗНЗЈНјааЛКДцЁЃ

НћгУИпЫйЛКДц: УПЕБАќКЌвЛВПЗжаТгІгУГЬађЕФЪ§ОнАќЕНДяЪБЃЌНЋЦфаДЕНЩСДцжаЕФФПБъЮЛжУЁЃ

ДЫЗНАИЗЧГЃМђЕЅЃЌПЩвдзюаЁЛЏ OTA ИќаТШэМўЕФТпМСПЃЌЕЋЪЧЫќвЊЧѓаТгІгУГЬађЕФЩСДцЧјгђБЛЭъШЋВСГ§ЁЃ етжжЗНЗЈЯїШѕСЫЩСДцЃЌдіМгСЫПЊЯњЁЃ

ВПЗжЛКДц: БЃСєвЛИі SRAM ЧјгђгУгкЛКДцЃЌЕБаТЪ§ОнАќЕНДяЪБНЋЫќУЧДцДЂдк

SRAM ЕФЧјгђжаЁЃ ЕБЧјгђЬюТњЪБЃЌЭЈЙ§НЋЪ§ОнаДШыПьЩСДцДЂЦїРДЧхПеЫќЁЃ ШчЙћЪ§ОнАќЮоађЕНДяЃЌЛђепдкаТЕФгІгУГЬађЖўНјжЦЮФМўжаДцдкМфЯЖЃЌетПЩФмЛсБфЕУКмИДдгЃЌвђЮЊашвЊвЛжжНЋ

SRAM ЕижЗгГЩфЕНЩСДцЕижЗЕФЗНЗЈЁЃ вЛжжВпТдЪЧНЋИпЫйЛКДцзїЮЊЩСДцЕФвЛВПЗжОЕЯёЁЃ ЩСДцЗжЮЊаЁЧјгђЕФвГУцЃЌетЪЧаДВйзїЕФзюаЁЛЎЗжЁЃ

гЩгкетжжздШЛЕФЛЎЗжЃЌвЛИіКУЕФЗНЗЈЪЧдк SRAM жаЛКДцвЛвГЩСДцЃЌЕБЫќЬюТњЛђепЯТвЛИіЪ§ОнАќЪєгкВЛЭЌЕФвГУцЪБЃЌЭЈЙ§аДИУвГУцЕФЩСДцРДЫЂаТЛКДцЁЃ

ЭъШЋЛКДц: дк OTA ИќаТЙ§ГЬжаЃЌНЋећИіаТгІгУГЬађДцДЂдк SRAM

жаЃЌВЂжЛдкДгЗўЮёЦїЭъШЋЯТдиКѓНЋЦфаДШыЩСДцЁЃ етжжЗНЗЈЭЈЙ§МѕЩйЖдЩСДцЕФаДШыДЮЪ§ЃЌБмУтСЫ OTA ИќаТШэМўИДдгЕФЛКДцТпМЃЌПЫЗўСЫвдЭљЗНЗЈЕФШБЕуЁЃ

ЕЋЪЧЃЌетНЋЯожЦЯТдиаТгІгУГЬађЕФДѓаЁЃЌвђЮЊЯЕЭГЩЯПЩгУ SRAM ЕФЪ§СПЭЈГЃдЖаЁгкПЩгУЩСДцЕФЪ§СПЁЃ

ЭМ5 РћгУ SRAM ЪЕЯжвЛвГИпЫйЛКДц

дк OTA ИќаТЙ§ГЬжаЪЙгУВПЗжЛКДцЕФЕкЖўжжЗНАИШчЭМ5ЫљЪОЃЌЦфжаЭМ3КЭЭМ4жагІгУГЬађ

a ЕФЩСДцВПЗжБЛЗХДѓЃЌЖј SSBL ЕФ SRAM ЙІФмДцДЂЦїгГЩфЭМдђШчЭМЫљЪОЁЃ ЯдЪОСЫвЛИі2 kB

ДѓаЁЕФ flash вГУцЪОР§ЁЃзюжеЃЌетИіЩшМЦОіВпНЋИљОнаТгІгУГЬађЕФДѓаЁКЭдЪаэЕФ OTA ИќаТШэМўЕФИДдгадРДШЗЖЈЁЃ

АВШЋМАЭЈаХ

ЩшМЦШЈКт: ШэМў vs авщ

OTAИќаТНтОіЗНАИЛЙБиаыНтОіАВШЋадКЭЭЈаХЮЪЬтЁЃ аэЖрРрЫЦгкЭМ1ЫљЪОЕФЯЕЭГНЋОпгадкгВМўКЭШэМўжаЪЕЯжЕФЭЈаХавщЃЌгУгке§ГЃЕФ(ЗЧOTAИќаТЯрЙиЕФ)ЯЕЭГааЮЊЃЌШчНЛЛЛДЋИаЦїЪ§ОнЁЃ

етвтЮЖзХдкЗўЮёЦїКЭПЭЛЇЛњжЎМфвбОНЈСЂСЫвЛжж(ПЩФмЪЧАВШЋЕФ)ЮоЯпЭЈаХЗНЗЈЁЃ ЯёЭМ1етбљЕФЧЖШыЪНЯЕЭГПЩФмЪЙгУЕФЭЈаХавщЃЌР§ШчЃЌBLEЛђ6LoWPANЁЃ

гаЪБетаЉавщжЇГжАВШЋадКЭЪ§ОнНЛЛЛЃЌOTAИќаТШэМўПЩвдИќаТЙ§ГЬжаРћгУетаЉАВШЋадКЭЪ§ОнНЛЛЛЁЃ

БиаыЙЙНЈ OTA ИќаТШэМўжаЕФЭЈаХЙІФмЃЌЕЋзюжеНЋШЁОігкЯжгаЭЈаХавщЬсЙЉСЫЖрЩйГщЯѓЁЃ

ЯжгаЕФЭЈаХавщЪЧдкЗўЮёЦїКЭПЭЛЇЛњжЎМфЗЂЫЭКЭНгЪеЮФМўЕФЙЄОпЃЌOTA ИќаТШэМўПЩвдМђЕЅЕиРћгУетаЉЙЄОпНјааЯТдиЁЃ

ШЛЖјЃЌШчЙћЭЈаХавщБШНЯдЪМЃЌВЂЧвжЛФмЗЂЫЭдЪМЪ§ОнЃЌдђ OTA ИќаТШэМўПЩФмашвЊжДааЗжАќЃЌВЂЫцаТЕФгІгУГЬађЖўНјжЦЮФМўЬсЙЉдЊЪ§ОнЁЃ

етвВЪЪгУгкАВШЋЬєеНЁЃ ШчЙћЭЈаХавщВЛжЇГжЃЌдђ OTA ИќаТШэМўПЩФмИКд№НтУмЭЈЙ§ПежаЗЂЫЭЕФгУгкБЃУмЕФзжНкЁЃ

змжЎЃЌЙЙНЈжюШчздЖЈвхАќНсЙЙЁЂЗўЮёЦї/ПЭЛЇЖЫЭЌВНЁЂМгУмКЭУмдПНЛЛЛЙІФмЃЌВЂАбЫќУЧЗПЕН

OTA ИќаТШэМўжаЕФЙЄОпНЋИљОнЯЕЭГЕФЭЈаХавщЬсЙЉЕФФкШнвдМАЖдАВШЋадКЭПЩППадЕФвЊЧѓРДШЗЖЈЁЃ

НтОіАВШЋЬєеН

АВШЋНтОіЗНАИашвЊЖдЭЈЙ§ПежаЗЂЫЭЕФаТгІгУГЬађБЃУмЃЌМьВтаТгІгУГЬађжаЕФШЮКЮЫ№ЛЕЃЌВЂбщжЄаТгІгУГЬађЪЧДгЪмаХШЮЕФЗўЮёЦїЗЂЫЭЕФЃЌЖјВЛЪЧДгЖёвтЗНЗЂЫЭЕФЁЃ

етаЉЬєеНПЩвдЭЈЙ§ЪЙгУМгУм(crypto)ВйзїРДНтОіЁЃ

ОпЬхРДЫЕЃЌПЩвддкАВШЋНтОіЗНАИжаЪЙгУСНжжГЦЮЊМгУмКЭЙўЯЃЕФМгУмВйзїЁЃ

МгУмММЪѕНЋдкПЭЛЇЖЫКЭЗўЮёЦїжЎМфЪЙгУвЛИіЙВЯэЕФУмдП(УмТы)РДЛьЯ§ЮоЯпДЋЪфЕФЪ§ОнЁЃ ЮЂПижЦЦїЕФУмТыгВМўМгЫйЦїПЩФмжЇГжЕФвЛжжЬиЪтРраЭЕФМгУмБЛГЦЮЊ

AES-128Лђ AES-256ЃЌетШЁОігкУмдПЕФДѓаЁЁЃ гыМгУмЕФЪ§ОнвЛЦ№ЃЌЗўЮёЦїПЩвдЗЂЫЭеЊвЊЃЌвдШЗБЃУЛгаЫ№ЛЕЁЃ

етИіеЊвЊЪЧЭЈЙ§ЩЂСаЪ§ОнАќ(вЛИіЩњГЩЮЈвЛДњТыЕФВЛПЩФцЪ§бЇКЏЪ§)ЩњГЩЕФЁЃ ШчЙћЯћЯЂЛђеЊвЊЕФШЮКЮВПЗждкЗўЮёЦїДДНЈЫќУЧжЎКѓБЛаоИФЃЌБШШчдкЮоЯпЭЈаХЦкМфгавЛИіЮЛБЛЗзЊЃЌЕБПЭЛЇЖЫЖдЪ§ОнАќжДааЯрЭЌЕФЙўЯЃКЏЪ§ВЂБШНЯеЊвЊЪБЃЌЫќЛсзЂвтЕНетИіаоИФЁЃ

ЮЂПижЦЦїЕФМгУмгВМўМгЫйЦїПЩФмжЇГжЕФвЛжжЬиЖЈРраЭЙўЯЃЗНЪНЪЧ SHA-256ЁЃ

ЭМ6ЯдЪОСЫЮЂПижЦЦїжаЕФМгУмгВМўЭтЩшЕФПђЭМЃЌOTA ИќаТШэМўЮЛгк Cortex-M4гІгУВуЁЃ ДЫЭМЛЙЯдЪОСЫЖдЭтЮЇЩшБИжаЕФЪмБЃЛЄУмдПДцДЂЕФжЇГжЃЌПЩвддк

OTA ИќаТШэМўНтОіЗНАИжаРћгУИУжЇГжРДАВШЋДцДЂПЭЛЇЖЫЕФУмдПЁЃ

ЭМ6 Лљгк ADuCM4050ЕФУмТыМгЫйЦїгВМўПђЭМ

ЪЙгУЗЧЖдГЦМгУмЪЧНтОіЩэЗнбщжЄзюКѓЬєеНЕФвЛжжГЃгУММЪѕЁЃ ЖдгкДЫВйзїЃЌЗўЮёЦїЩњГЩвЛИіЙЋЫНУмдПЖдЁЃжЛгаЗўЮёЦїжЊЕРЫНдПЃЌЖјПЭЛЇЛњжЊЕРЙЋдПЁЃ

ЪЙгУЫНдПЃЌЗўЮёЦїПЩвдЩњГЩИјЖЈЪ§ОнПщЕФЧЉУћЁЊЁЊОЭЯёНЋЭЈЙ§ЮоЯпЗНЪНЗЂЫЭЕФАќЕФеЊвЊвЛбљЁЃ ЧЉУћБЛЗЂЫЭЕНПЭЛЇЖЫЃЌПЭЛЇЖЫПЩвдЪЙгУЙЋдПбщжЄЧЉУћЁЃ

етЪЙПЭЛЇЛњФмЙЛШЗШЯЯћЯЂЪЧДгЗўЮёЦїЗЂГіЕФЃЌЖјВЛЪЧгЩСїУЅЕкШ§ЗНЗЂГіЕФЁЃ етИіађСаШчЭМ7ЫљЪОЃЌгУЪЕМ§ЭЗБэЪОКЏЪ§ЕФЪфШы

/ ЪфГіЃЌгУащМ§ЭЗБэЪОЭЈЙ§ПежаЗЂЫЭЕФаХЯЂЁЃ

ЭМ7 ЪЙгУЗЧЖдГЦМгУмЖдЯћЯЂНјааЩэЗнбщжЄ

ДѓЖрЪ§ЮЂПижЦЦїУЛгагВМўМгЫйЦїРДЪЕЯжетаЉЗЧЖдГЦМгУмВйзїЃЌЕЋПЩвдЪЙгУжюШч

Micro-ECC ЕШШэМўПтРДЪЕЯжЃЌетаЉШэМўПтзЈУХеыЖдзЪдДЪмЯоЕФЩшБИЁЃПташвЊвЛИігУЛЇЖЈвхЕФЫцЛњЪ§ФИКЏЪ§ЃЌетПЩвдЪЕЯжЪЙгУецЫцЛњЪ§ЗЂЩњЦїЕФгВМўЭтЮЇЕФЮЂПижЦЦїЁЃ

ОЁЙметаЉЗЧЖдГЦМгУмВйзїНтОіСЫ OTA ИќаТЙ§ГЬжаЕФаХШЮЮЪЬтЃЌЕЋЫќУЧдкДІРэЪБМфЗНУцДњМлИпАКЃЌЖјЧвашвЊНЋЧЉУћгыЪ§ОнвЛЦ№ЗЂЫЭЃЌетдіМгСЫЪ§ОнАќЕФДѓаЁЁЃ

ПЩвддкЯТдиНсЪјЪБжДаавЛДЮМьВщЃЌЪЙгУзюжеАќЕФеЊвЊЛђећИіаТШэМўгІгУГЬађЕФеЊвЊЃЌЕЋетНЋдЪаэЕкШ§ЗНЯТдиВЛЪмаХШЮЕФШэМўЕНПЭЛЇЖЫЃЌетВЂВЛРэЯыЁЃ

РэЯыЧщПіЯТЃЌЯЃЭћбщжЄЫљЪеЕНЕФУПИіЪ§ОнАќЖМЪЧРДздЪмаХШЮЕФЗўЮёЦїЃЌЖјЧвУПДЮЖМВЛашвЊЧЉУћЕФПЊЯњЁЃ етПЩвдЭЈЙ§ЙўЯЃСДРДЪЕЯжЁЃ

ЙўЯЃСДНЋетРяЬжТлЕФМгУмИХФюКЯВЂЮЊвЛЯЕСаЪ§ОнАќЃЌДгЖјЪЕЯжЪ§бЇЩЯЕФСЌНгЁЃ

ШчЭМ8ЫљЪОЃЌЕквЛИіАќ(Ъ§зж0)АќКЌЯТвЛИіАќЕФеЊвЊЁЃ гыЪЕМЪЕФШэМўгІгУГЬађЪ§ОнВЛЭЌЃЌЕквЛИіЪ§ОнАќЕФИКдиЪЧЧЉУћЁЃ

ЕкЖўИіАќ(БрКХ1)гааЇИКдиАќКЌЖўНјжЦЕФвЛВПЗжКЭЕкШ§ИіАќЕФеЊвЊ(БрКХ2)ЁЃ ПЭЛЇЖЫбщжЄЕквЛИіЪ§ОнАќжаЕФЧЉУћЃЌВЂЛКДцеЊвЊ

H0ЃЌвдЙЉвдКѓЪЙгУЁЃ ЕБЕкЖўИіЪ§ОнАќЕНДяЪБЃЌПЭЛЇЖЫЙўЯЃИКдиВЂНЋЦфгы H0НјааБШНЯЁЃ ШчЙћЫќУЧЦЅХфЃЌПЭЛЇЖЫПЩвдШЗЖЈетИіКѓајЪ§ОнАќРДздЪмаХШЮЕФЗўЮёЦїЃЌЖјВЛашвЊНјааЧЉУћМьВщЁЃ

ЩњГЩетИіСДЕФДњМлИпАКЕФШЮЮёСєИјСЫЗўЮёЦїЃЌЕБУПИіЪ§ОнАќЕНДяЪБЃЌПЭЛЇЛњБиаыМђЕЅЕиЛКДцКЭЙўЯЃЃЌвдШЗБЃЪ§ОнАќЕНДяЪБУЛгаЫ№ЛЕЃЌОпгаЭъећадЃЌВЂОЙ§бщжЄЁЃ

ЭМ8 НЋЙўЯЃСДгІгУгкАќађСа

ЪЕбщбщжЄ

БОЮФжаЬсЕНЕФНтОіДцДЂЦїЁЂЭЈаХКЭАВШЋЩшМЦФбЬтЕФГЌЕЭЙІКФЮЂПижЦЦїЪЧ ADuCM3029КЭ

ADuCM4050ЁЃ етаЉЮЂПижЦЦїАќКЌЮЊ OTA ИќаТЬжТлЕФгВМўЭтЩшЃЌШчЩСДцЁЂ SRAMЁЂМгУмМгЫйЦїКЭеце§ЕФЫцЛњЪ§ЗЂЩњЦїЁЃ

гУгкетаЉЮЂПижЦЦїЕФЩшБИМвзхАќ(DFP)ЮЊдкетаЉЩшБИЩЯЙЙНЈ OTA ИќаТНтОіЗНАИЬсЙЉШэМўжЇГжЁЃ DFPАќКЌЭтЮЇЧ§ЖЏГЬађЃЌЮЊгВМўЬсЙЉСЫМђЕЅЁЂСщЛюЕФНгПкЁЃ

гВМўХфжУ

ЮЊСЫбщжЄетРяЬжТлЕФИХФюЃЌЪЙгУ ADuCM4050ДДНЈСЫвЛИі OTA

update ШэМўВЮПМЩшМЦЁЃ ЖдгкПЭЛЇЖЫЃЌADuCM4050 EZ-KIT ЭЈЙ§ЪЙгУЮоЯпЪеЗЂЦїСЌНгЕН

ADF7242ЁЃ ПЭЛЇЛњЩшБИШчЭМ9ЫљЪОЁЃ ЖдгкЗўЮёЦїЃЌПЊЗЂСЫвЛИідк Windows PC ЩЯдЫааЕФ

Python гІгУГЬађЁЃ Python гІгУГЬађЭЈЙ§ДЎааЖЫПкгыСэвЛИі ADuCM4050 EZ-KIT

НјааЭЈаХЃЌКѓепвВга ADF7242гыПЭЛЇЖЫЯрЭЌЕФЩшжУЁЃ ШЛЖјЃЌЭМ9жагвБпЕФ EZ-KIT ВЛжДаа OTA

ИќаТТпМЃЌжЛЪЧНЋДгADF7242ЪеЕНЕФЪ§ОнАќзЊЗЂИј Python гІгУГЬађЁЃ

ЭМ9 ЪЕбщадгВМўЩшжУ

ШэМўзщМў

ШчЭМ3ЫљЪОЕФШэМўВЮПМЩшМЦЖдПЭЛЇЖЫЩшБИЕФЩСДцНјааЗжЧјЁЃ жївЊЕФПЭЛЇЖЫгІгУГЬађБЛЩшМЦЮЊПЩвЦжВКЭПЩХфжУЕФЃЌетбљОЭПЩвддкЦфЫћХфжУЛђЦфЫћгВМўЦНЬЈЩЯЪЙгУЁЃ

ЭМ10ЯдЪОСЫПЭЛЇЖЫЩшБИЕФШэМўМмЙЙЁЃЧызЂвтЃЌЫфШЛгаЪБНЋећИігІгУГЬађГЦЮЊ SSBLЃЌЕЋЪЧдкЭМ10жавдМАДгЯждкПЊЪМЃЌДгТпМЩЯНЋеце§ЕФ

SSBL ВПЗж(РЖЩЋ)гы OTA ИќаТВПЗж(КьЩЋ)ЗжПЊЃЌвђЮЊКѓепВЛвЛЖЈашвЊЯёЧАУцЬжТлЕФФЧбљЭъШЋдкЭЌвЛИігІгУГЬађжаЪЕЯжЁЃ

ЭМ10ЫљЪОЕФгВМўГщЯѓВуВуБЃГжСЫ OTA ПЭЛЇЖЫШэМўЕФПЩвЦжВадЃЌВЂЧвЖРСЂгкШЮКЮЕзВуПт(ШчГШЩЋЫљЪО)ЁЃ

ЭМ10 ПЭЛЇЖЫШэМўЬхЯЕМмЙЙ

ШэМўгІгУГЬађЪЕЯжСЫЭМ3жаЕФв§ЕМађСаЃЌвЛИіДгЗўЮёЦїЯТдиаТгІгУГЬађЕФМђЕЅЭЈаХавщЃЌвдМАЙўЯЃСДЁЃ

ЭЈаХавщжаЕФУПИіЪ§ОнАќЖМга12зжНкЕФдЊЪ§ОнЭЗЁЂ64зжНкЕФгааЇИКдиКЭ32зжНкЕФеЊвЊЁЃДЫЭтЃЌЫќЛЙОпгавдЯТЬиЕу:

ЛКДц: жЇГжВЛЛКДцЛђЛКДцвЛвГЩСДцЃЌОпЬхШЁОігкгУЛЇХфжУЁЃ

ФПТМ: ToC БЛЩшМЦгУгкжЛБЃДцСНИігІгУГЬађЃЌВЂЧваТЕФгІгУГЬађзмЪЧБЛЯТдиЕНзюРЯЕФЮЛжУЃЌвдБЃСєвЛИіЛиЭЫгІгУГЬађЁЃ

етОЭЪЧЫљЮНЕФ A/BИќаТЗНАИЁЃ

ЯћЯЂДЋЕн: ИљОнгУЛЇХфжУЃЌЖдЯћЯЂДЋЕнЕФ ADF7242Лђ UART

ЬсЙЉжЇГжЁЃ ЪЙгУ UART НјааЯћЯЂДЋЕнЯћГ§СЫЭМ9жазѓБпЕФ EZ-KITЃЌЪЙЕУгвБпЕФВПЗжСєИјСЫПЭЛЇЖЫЁЃ

етжждкЯпИќаТЗНАИЖдгкГѕЪМЛЏЯЕЭГКЭЕїЪдЗЧГЃгагУЁЃ

ЪЕбщНсЙћ

Г§СЫТњзуЙІФмашЧѓКЭЭЈЙ§ИїжжВтЪджЎЭтЃЌШэМўЕФадФмвВЪЧОіЖЈЯюФПГЩЙІгыЗёЕФЙиМќЁЃ

СНИіЭЈГЃгУРДКтСПЧЖШыЪНШэМўадФмЕФжИБъЪЧеМгУПеМфКЭжИСюжмЦкЁЃ еМгУПеМфЪЧжИШэМўгІгУГЬађдкSRAMКЭFlashжаеМгУЕФПеМфЁЃ

жИСюжмЦкЪЧжИШэМўгУРДжДааЬиЖЈШЮЮёЕФЮЂДІРэЦїЪБжгжмЦкЪ§ЁЃ ЫфШЛЫќРрЫЦгкШэМўдЫааЪБЃЌЕЋЫќНтЪЭСЫетбљвЛИіЪТЪЕЃЌМДдкНјаа

OTA ИќаТЪБЃЌШэМўПЩФмЛсНјШыЕЭЙІКФФЃЪНЃЌвђЮЊдкФЧРяЮЂДІРэЦїЪЧЗЧЛюЖЏЕФЃЌВЂЧвУЛгаЯћКФжмЦкЁЃ ЫфШЛШэМўВЮПМЩшМЦУЛгаеыЖдетСНИіЖШСПБъзМНјаагХЛЏЃЌЕЋЪЧЫќУЧЖдгкВтЪдГЬађКЭБШНЯЩшМЦШЈКтЖМЪЧгагУЕФЁЃ

ЭМ11КЭЭМ12ЯдЪОСЫ OTA ИќаТШэМўВЮПМЩшМЦдк ADuCM4050ЩЯЪЕЯжЕФФкДцДѓаЁЃЌВЛЪЙгУЛКДцЁЃ

етаЉЪ§зжЪЧИљОнЭМ10ЫљЪОЕФзщМўНјааЗжЧјЕФЁЃ ШчЭМ11ЫљЪОЃЌећИігІгУГЬађЪЙгУдМ15kb ЕФЩСДцЁЃ ПМТЧЕН

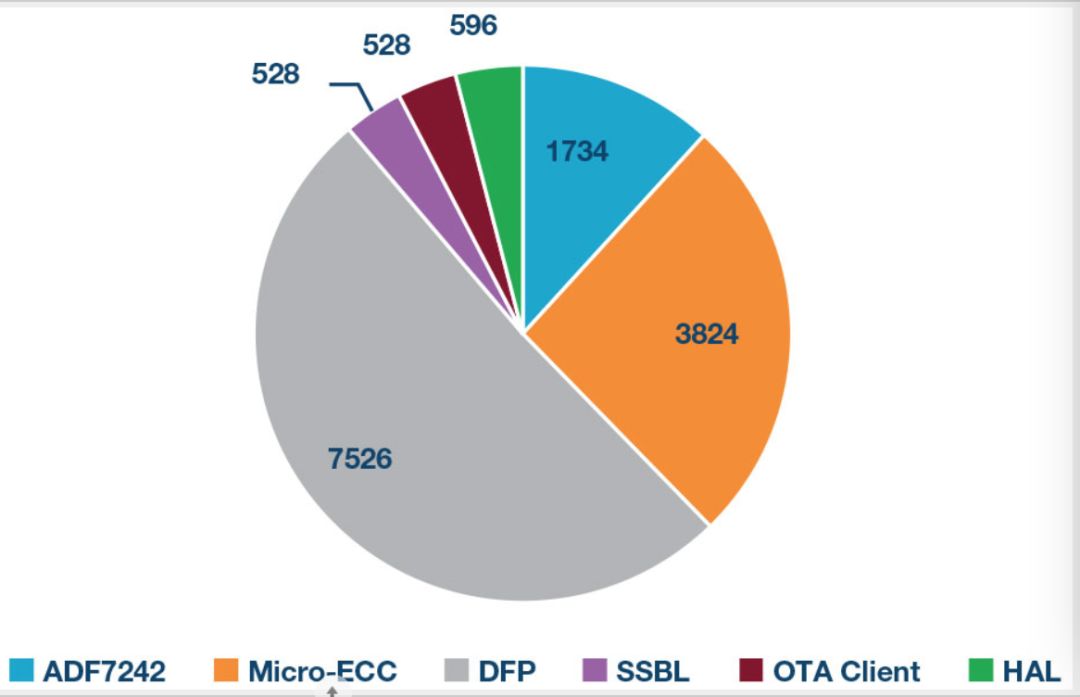

ADuCM4050АќКЌ512kb ЕФЩСДцЃЌетИіЪ§ОнЬЋаЁСЫЁЃ еце§ЕФгІгУШэМў(ЮЊOTAИќаТЙ§ГЬПЊЗЂЕФШэМў)жЛашвЊ1.5

kB зѓгвЃЌЦфгрВПЗжгУгк DFPЁЂ Micro-ECC КЭ ADF7242ЖбеЛЕШПтЁЃ етаЉНсЙћгажњгкЫЕУї

SSBL дкЯЕЭГжагІИУАчбнЕФНЧЩЋЕФЩшМЦШЈКтЁЃ ДѓЖрЪ§15 kB ЕФФкДцеМгУгУгкИќаТЙ§ГЬЁЃ SSBLБОЩэжЛеМгУДѓдМ500ИізжНкЕФФкДцПеМфЃЌСэЭтЛЙга1ЕН2

kB ЕФ DFP ДњТыгУгкЩшБИЗУЮЪЃЌБШШч Flash Ч§ЖЏГЬађЁЃ

ЭМ11 ЩСДцеМгУПеМф(зжНк)

ЭМ12 SRAMеМгУПеМф(зжНк)

ЮЊСЫЦРЙРШэМўЕФПЊЯњЃЌдкУПДЮЪеЕНЪ§ОнАќЪБжДаажИСюжмЦкМЦЪ§ЃЌШЛКѓВщПДУПИіАќЫљЯћКФЕФЦНОљжИСюжмЦкЪ§ЁЃ

УПИіЪ§ОнАќЖМашвЊ AES-128НтУмЁЂ SHA-256ЩЂСаЁЂЖдЩСДцЕФаДШывдМАвЛаЉАќЕФдЊЪ§ОнбщжЄЁЃ дкЪ§ОнАќгааЇИКдиЮЊ64зжНкЧвУЛгаЛКДцЕФЧщПіЯТЃЌДІРэЕЅИіЪ§ОнАќЕФПЊЯњЮЊ7409жмЦкЁЃ

ЪЙгУ26MhzЪБжгЃЌДІРэЪБМфдМЮЊ285ЮЂУыЁЃ ИУжЕЪЧЪЙгУЮЛгк ADuCM4050 DFP (ЮДЕїећжмЦк)ЕФбЛЗМЦЪ§Ч§ЖЏГЬађМЦЫуЕФЃЌЪЧ100kb

ЖўНјжЦЯТди(ДѓдМ1500ИіЪ§ОнАќ)ЦкМфЕФЦНОљжЕЁЃ?

УПИіАќЕФзюаЁПЊЯњПЩЙщвђгк DFP жаЕФЧ§ЖЏГЬађдкжДаазмЯпЪТЮёЪБРћгУ

ADuCM4050ЩЯЕФжБНгФкДцЗУЮЪ(DMA)гВМўЭтЩшЃЌвдМАЧ§ЖЏГЬађдкУПИіЪТЮёЦкМфНЋДІРэЦїжУгкЕЭЙІКФЫЏУпзДЬЌЁЃ

ШчЙћНћгУ DFP жаЕФЕЭЙІКФанУпЃЌВЂНЋзмЯпЪТЮёИФЮЊВЛЪЙгУ DMAЃЌФЧУДУПИіЪ§ОнАќЕФПЊЯњНЋдіМгЕН17,297ИіжмЦкЁЃ

етЫЕУїСЫЩшБИЧ§ЖЏГЬађЕФгааЇЪЙгУЖдЧЖШыЪНШэМўгІгУГЬађЕФгАЯьЁЃ ЫфШЛУПИіЪ§ОнАќЕФЪ§ОнзжНкЪ§КмЩйЃЌвђДЫПЊЯњвВКмЕЭЃЌЕЋЪЧУПИіЪ§ОнАќЕФЪ§ОнзжНкЪ§діМгвЛБЖЃЌДяЕН128ЃЌжЛЛсдкбЛЗжаВњЩњвЛИіаЁЕФдіГЄЃЌвђДЫЖдгкЭЌбљЕФЪЕбщЃЌашвЊ8,362ИіжИСюжмЦкЁЃ

жИСюжмЦкКЭеМгУПеМфЛЙЫЕУїСЫЧАУцЬжТлЕФЛКДцАќЪ§ОнЖјВЛЪЧУПДЮаДШыЩСДцЕФШЈКтЁЃ

ЦєгУвЛвГЩСДцЛКДцКѓЃЌУПИіЪ§ОнАќЕФПЊЯњДг7,409МѕЩйЕН5,904ИіжмЦкЁЃ ет20% ЕФМѕЩйЪЧгЩгкЖдДѓЖрЪ§АќЬјЙ§СЫFlash

аДВйзїЃЌВЂЧвжЛдкЛКДцТњЕФЪБКђжДаавЛДЮFlash аДВйзїЁЃ етжжМѕЩйЪЧвдSRAMЮЊДњМлЕФЁЃ ШчЙћУЛгаЛКДцЃЌHALжЛашвЊ336ИізжНкЕФ

SRAMЃЌШчЭМ12ЫљЪОЁЃ ШЛЖјЃЌЕБЪЙгУЛКДцЪБЃЌБиаыБЃСєЯрЕБгквЛећвГЩСДцЕФПеМфЃЌетНЋ SRAM ЕФРћгУТЪдіМгЕН2,388ИізжНкЁЃ

HAL ЕФЩСДцРћгУТЪвВТдгаЬсИпЃЌвђЮЊашвЊЖюЭтЕФДњТыРДОіЖЈЪВУДЪБКђБиаыЫЂаТЛКДцЁЃ

етаЉНсЙћжЄУїСЫЩшМЦОіВпЖдШэМўадФмЕФЧаЪЕгАЯьЁЃ УЛгаЗХжЎЫФКЃЖјНдзМЕФНтОіЗНАИЉ`Љ`УПИіЯЕЭГЖМгаВЛЭЌЕФашЧѓКЭЯожЦЃЌЖјЧв

OTA ЕФИќаТШэМўашвЊНјааЕїећвдНтОіетаЉЮЪЬтЁЃ ЯЃЭћБОЮФЖдЩшМЦЁЂЪЕЯжКЭбщжЄ OTA ИќаТШэМўНтОіЗНАИЪБгіЕНЕФвЛаЉГЃМћЮЪЬтКЭНтОіЗНАИЬсЙЉвЛаЉАяжњЃЌеце§ХЊЖЎШчКЮЪЕЯжЮяСЊЭјЩшБИЕФOTAЁЃ

---------------------

|